9–17

AM700 Audio Measurement Set Service Manual

3

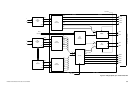

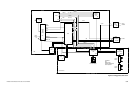

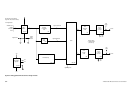

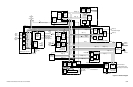

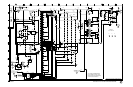

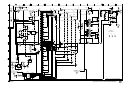

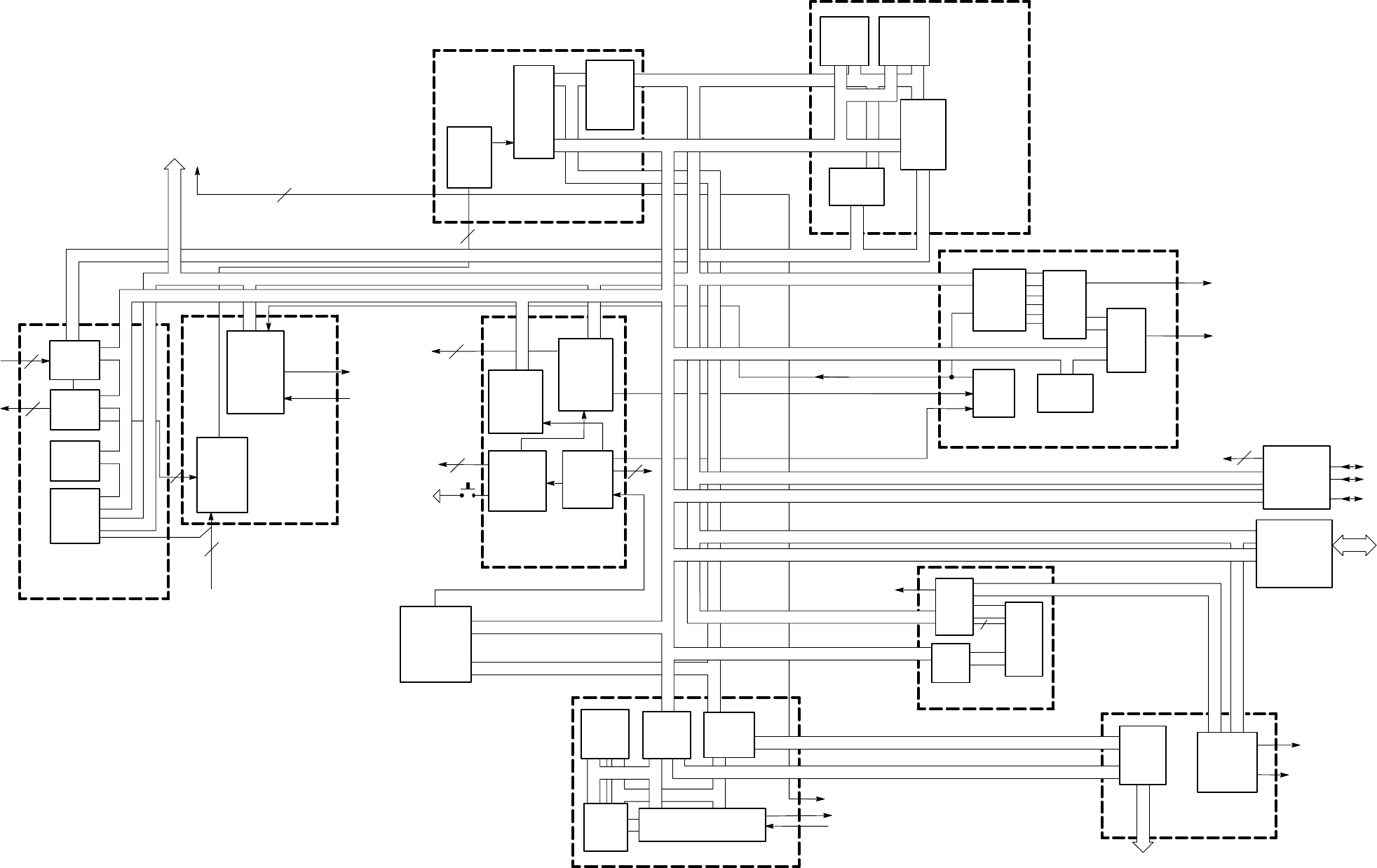

CPU and DSP Bus Interface

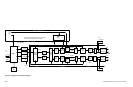

NVRAM

DRAM and Diagnostic Display

To VGA Monitor

To Internal Monitor (CRT)

Video ASIC and VRAM

To Front Panel Board

EPROM

ILP0 – ILP2

CPU

ADS[0 – 31]

ADS[0 – 31]

23

Timer

Reset

7

9

PWRDY

DRAM

CK8–0

15

TMIRQ

12

31

DPD[0 – 3]

ERR[0 – 3]

To Board Status Register

FA[0 – 17]

FD[0 – 15]

DB[0 – 31]

DB[0 – 31]

FPD[0 – 7]

CLICK

TIMOUT

DB[0 – 31]

Latch Control Signals

5

VRAM

B[0 – 7]

QADS[0 – 31]

QADS[0 – 31]

DB[0 – 31]

12

VDOIRQ

To Floppy Disk Drive

QADS[0 – 31]

IRQRS

2

U64

U65

U80 – 83

U79, U128

U34

U25 – 26

U44, U53

U41

QADS[0 – 31]

DB[0 – 31]

DB[0 – 31]

QADS[0 – 31]

FPD[0 – 7]

System Clock and Resets

Floppy

Board

Status

Inputs

Board

Board

Progam

outputs

Status

Register

Board

Program

Register

Board

Code

Register

Real

Time

Clock

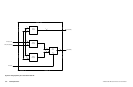

Board Registers and Timer

To

DSP DMA

and

Host Interface

Bus

Arbitration

PALS

Interrupt

Encoder

Interrupt

Requests

7 Levels

(IRQ1 – IRQ7)

+DSP

Host Bus

Bus

Arbitration

and

Interrupt

Encoder

and

Power Supply

Connectors

Bus Arbitration

Control Signals Out

Bus Arbitration

Control Signals In

Chip

Selects

and

Control Strobes

System

Resets

Master

Reset

Interrupt

Register

Bus

Buffers

U73,

U74 – 76,

U89

Address

Decoder

System

Clock

U27D,

U54D,

U59B,U60

U47,U49,

U135

Floppy

Drive

Memory

Data

Bus

Buffers

Address

Buffers

FP

Control

PAL

Front Panel Processor

I/O Processor

Latch Control Signals

4–Wire

Interface

Memory

Controller

Flash

EPROM

Memory Controller,

EPROM,FEPROM

and NVRAM

DRAM

Controller

Bus

Timeout

Diagnostic

Display

DRAM

Buffers

Video

ASIC

VRAM

Buffer

RS–232C

Interface

GPIB Controller

and

Host Interface

To RS232

Connector

To Keyboard

Connector

To

GPIB

Port

Connector

VRAM DAC and Floppy

Drive Interface

VRAM

DAC

Drive

Interface

Counter and

Address Decoder

or Display Driver (Flat Panel)

Figure 9–13: CPU block diagram