Intel® PXA255 Processor Developer’s Manual 3-27

Clocks and Power Manager

3.5.5 Power Manager Falling-Edge Detect Enable Register

(PFER)

The PFER, Table 3-11, determines if the GPIO pin enabled with the PWER causes a wake up from

sleep mode on that GPIO pin’s falling edge. When PWER[IDAE] is zero and a fault condition is

detected on the nVDD_FAULT or nBATT_FAULT pin, PFER is set to 0x0000_0003. This enables

falling edges on GP[1:0] to act as wake up sources. When PWER[IDAE] is set, fault conditions on

the nVDD_FAULT or nBATT_FAULT pins do not affect wake-up sources. PFER is also set to

0x0000_0003 during hardware, watchdog, and GPIO resets.

Software should enable wakeups only for those GPIO pins that are configured as inputs during

sleep. Any GPIO pins that are configured as outputs during sleep, should have their associated

wake enable bits set to logic zero in all three PMU wake enable registers (PWER, PRER, and

PFER).

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

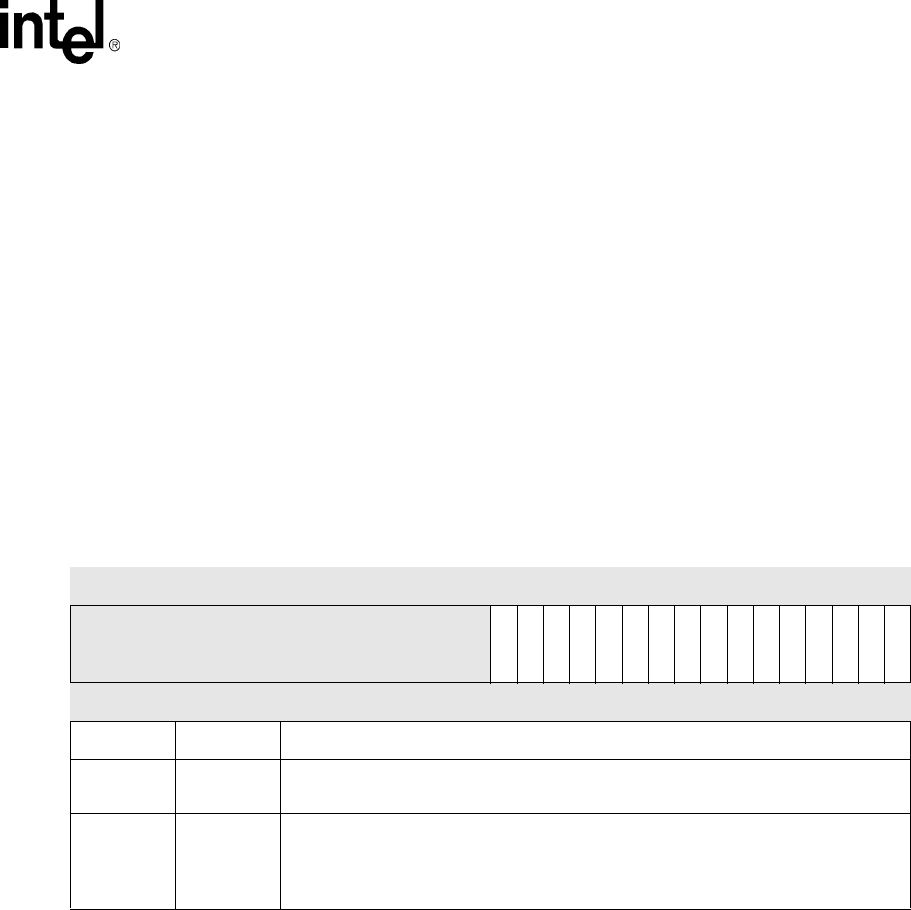

Table 3-11. PFER Bit Definitions

0x40F0_0014 PFER Clocks and Power Manager

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

FE15

FE14

FE13

FE12

FE11

FE10

FE9

FE8

FE7

FE6

FE5

FE4

FE3

FE2

FE1

FE0

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1

Bits Name Description

[31:16] —

Reserved.

Read undefined and must always be written with zeroes.

[15:0] FEx

Sleep mode Falling-edge Wake-up Enable

0 – Wake up due to GPx falling-edge detect disabled.

1 – Wake up due to GPx falling-edge detect enabled.

Set to 0x0003 on hardware, watchdog, and GPIO resets.