2-2 Intel® PXA255 Processor Developer’s Manual

System Architecture

2.2 Intel XScale® Microarchitecture Implementation

Options

The processor incorporates the Intel XScale® microarchitecture which is described in a separate

document. This core contains implementation options which an Application Specific Standard

Product (ASSP) may elect to implement or omit. This section describes those options.

Most of these options are specified within the coprocessor register space. The processor does not

implement any coprocessor registers beyond those defined in the Intel XScale® microarchitecture.

The coprocessor registers which are ASSP specific, as stated in the Intel XScale®

Microarchitecture for the Intel® PXA255 Processor User’s Manual, order number 278793, are

defined in the following sections.

2.2.1 Coprocessor 7 Register 4 - PSFS Bit

Bit 5 of this register is defined as the Power Source Fault Status bit or PSFS bit. This bit is set when

either nVDD_FAULT or nBATT_FAULT pins are asserted and the Imprecise Data Abort Enable

(IDAE) bit in the Power Manager Control Register (PMCR) is set.

This is a read-only register. Ignore reads from reserved bits.

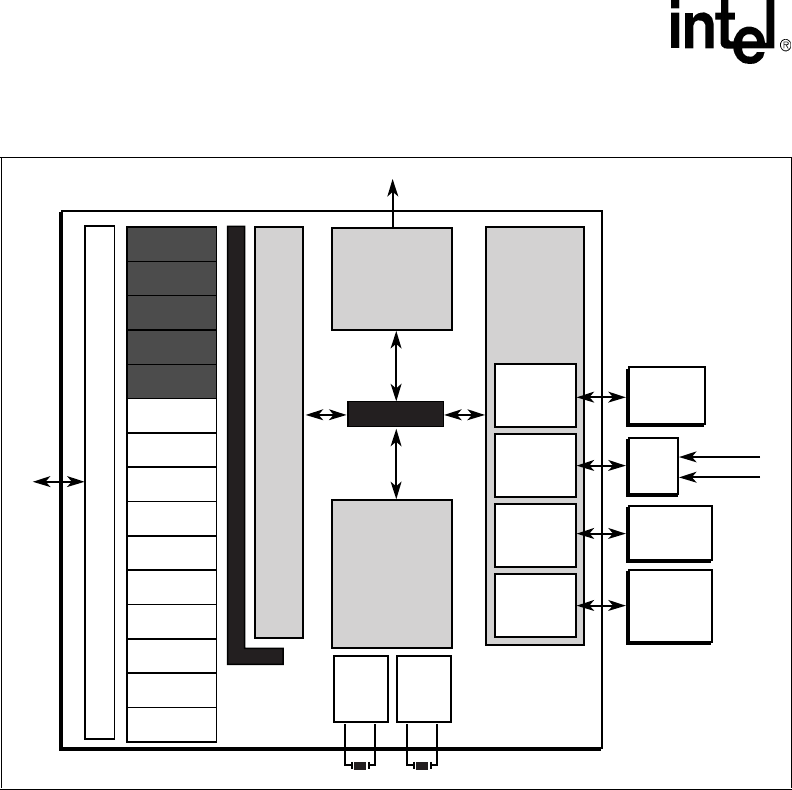

Figure 2-1. Block Diagram

Intelfi XScale

Microarchitecture

Color or

Grayscale

LCD

Controller

RTC

OS Timer

PWM(2)

Int.

Controller

Clocks &

Power Man.

I

2

S

AC97

UARTs

NSSP

Slow IrDA

SSP

USB

Client

General Purpose I/O

ASIC

Socket

0

Socket

1

3.6864

MHz

Osc

32.768

KHz

Osc

DMA Controller

and Bridge

XCVR

SDRAM/

SMROM

4 banks

ROM/

Flash/

SRAM

4 banks

I

2

C

Fast IrDA

MMC

Peripheral Bus

System Bus

Memory

Controller

Variable

Latency I/O

Control

PCMCIA

& CF

Control

Dynamic

Memory

Control

Static

Memory

Control