Intel® PXA255 Processor Developer’s Manual 12-29

USB Device Controller

12.6.4.8 Transmit Short Packet (TSP)

The software uses the transmit short packet bit to indicate that the last byte of a data transfer to the

FIFO has occurred. This indicates to the UDC that a short packet or zero-sized packet is ready to

transmit. Software must not set this bit if a 64-byte packet is to be transmitted. When the data

packet is successful transmitted, the UDC clears this bit.

These are read/write registers. Ignore reads from reserved bits. Write zeros to reserved bits.

12.6.5 UDC Endpoint x Control/Status Register (UDCCS2/7/12)

UDCCS2/7/12, shown in Table 12-16, contains 7 bits that are used to operate endpoint x, a Bulk

OUT endpoint.

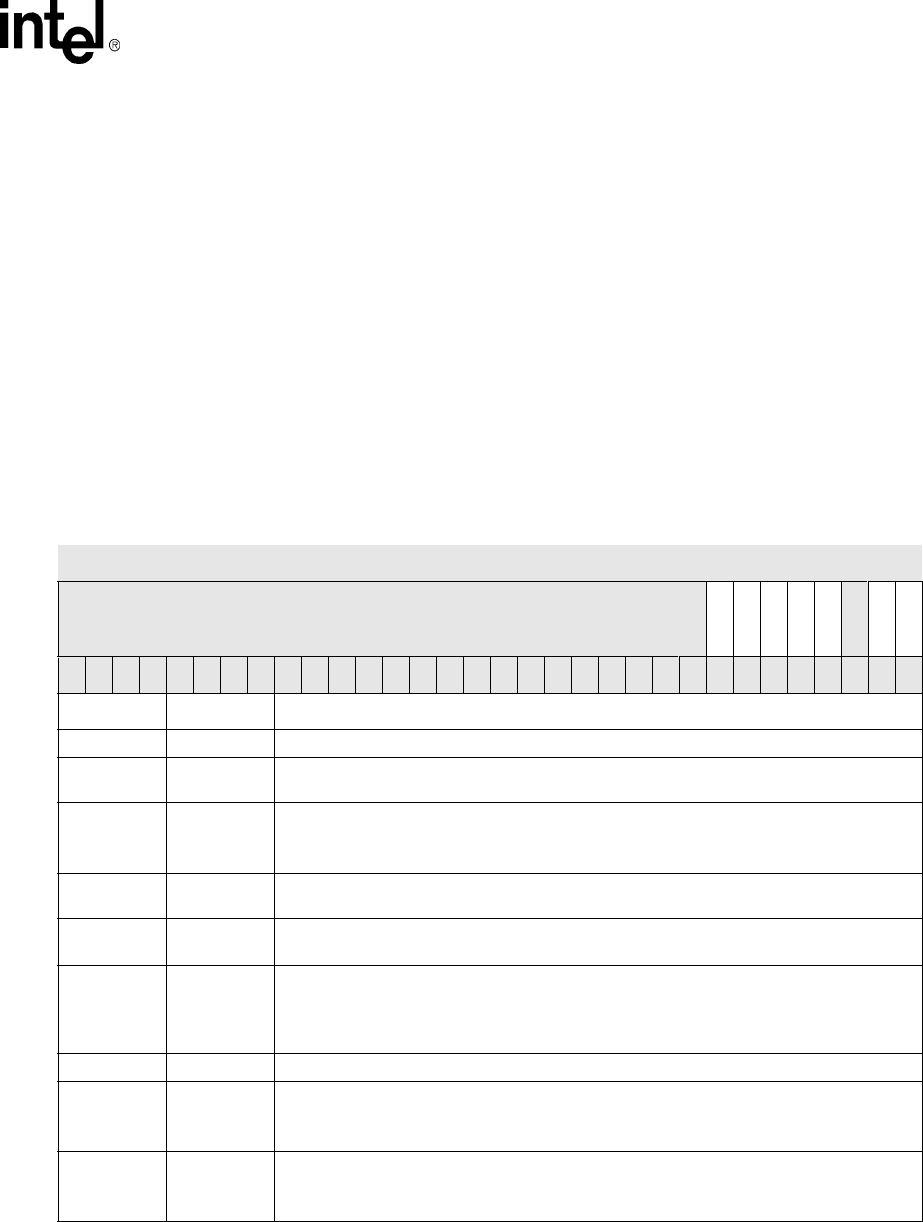

Table 12-16. UDCCS2/7/12 Bit Definitions

0x 4060_0018

0x 4060_002C

0x 4060_0040

UDCCS2

UDCCS7

UDCCS12

USB Device Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

RSP

RNE

FST

SST

DME

reserved

RPC

RFS

x x x x x x x x x x x x x x x x x x x x x x x x 0 0 0 0 0 0 0 0

Bit Name Description

31:8 — reserved

7RSP

Receive short packet (read-only).

1 = Short packet received and ready for reading.

6RNE

Receive FIFO not empty (read-only).

0 = Receive FIFO empty.

1 = Receive FIFO not empty.

5FST

Force stall (read/write).

1 = Issue STALL handshakes to OUT tokens.

4SST

Sent stall (read/write 1 to clear).

1 = STALL handshake was sent.

3DME

DMA Enable(read/write)

0 = Send data received interrupt after EOP received

1 = Send data received interrupt after EOP received and Receive FIFO has < 32 bytes of

data

2 — reserved

1RPC

Receive packet complete (read/write 1 to clear).

0 = Error/status bits invalid.

1 = Receive packet has been received and error/status bits are valid.

0RFS

Receive FIFO service (read-only).

0 = Receive FIFO has less than 1 data packet.

1 = Receive FIFO has 1 or more data packets.