17-10 Intel® PXA255 Processor Developer’s Manual

Hardware UART

17.5 Register Descriptions

17.5.1 Receive Buffer Register (RBR)

In non-FIFO mode, the RBR, shown in Table 17-2, holds the character(s) received by the UART’s

Receive Shift Register. If the RBR is configured to use fewer than eight bits, the bits are right-

justified and the most significant bits (MSB) are zeroed. Reading the register empties the register

and clears LSR[DR] (refer to Section 17.5.11, “Line Status Register (LSR)” on page 17-19).

In FIFO mode, the RBR latches the value of the data byte at the front of the FIFO (see Table 17-2).

This is a write-only register. Write zeros to reserve bits.

17.5.2 Transmit Holding Register (THR)

In non-FIFO mode, the THR, shown in Table 17-3, holds the next data byte(s) to be transmitted.

When the transmit shift register (TSR) is emptied, the contents of the THR are loaded in the TSR

and the LSR[TDRQ] is set to 1 (refer to Section 17.5.15).

In FIFO mode, a write to the THR puts data into the end of the FIFO. The data at the front of the

FIFO is loaded to the TSR when that register is empty.

This is a write-only register. Write zeros to reserve bits.

17.5.3 Divisor Latch Registers (DLL and DLH)

The HWUART contains a programmable baud rate generator that can take the 14.7456 MHz fixed

input clock and divide it by a number that is between 1 and 2

16

–1. The baud rate generator output

frequency is 16 times the baud rate. Two 8-bit latches store the divisor in a 16-bit binary format.

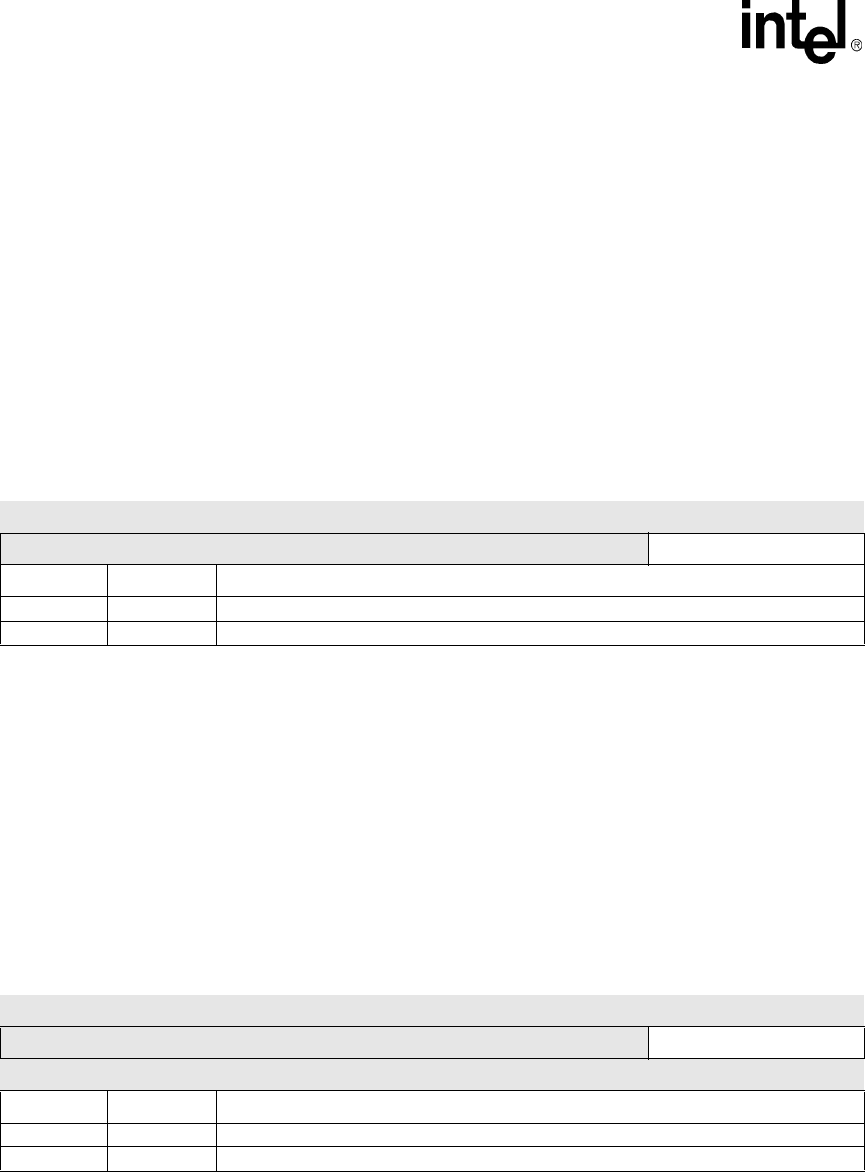

Table 17-2. RBR Bit Definitions

Physical Address

0x4160_0000 (DLAB=0)

Read Buffer Register (RBR) PXA255 Processor Hardware UART

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved Byte 0

Bits Name Description

31:8 — reserved

7:0 Byte 0 Byte 0

Table 17-3. THR Bit Definitions

Physical Address

0x4160_0000 (DLAB=0)

Transmit Holding Register (THR) PXA255 Processor Hardware UART

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved Byte 0

Reset

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 0 0 0 0 0 0 0 0

Bits Name Description

31:8 — reserved

7:0 Byte 0 Byte 0