Intel® PXA255 Processor Developer’s Manual 14-9

Inter-Integrated-Circuit Sound (I2S) Controller

14.6.1.1 Special purpose FIFO Read/Write function

As shown in Table 14-4, EFWR and STRF can be programmed for special purpose FIFO accesses.

Under normal operating conditions, the processor or the DMA controller can only write to the

Transmit FIFO and only read the Receive FIFO. Programming these bits allows the processor or

the DMA controller to read and write both FIFOs.

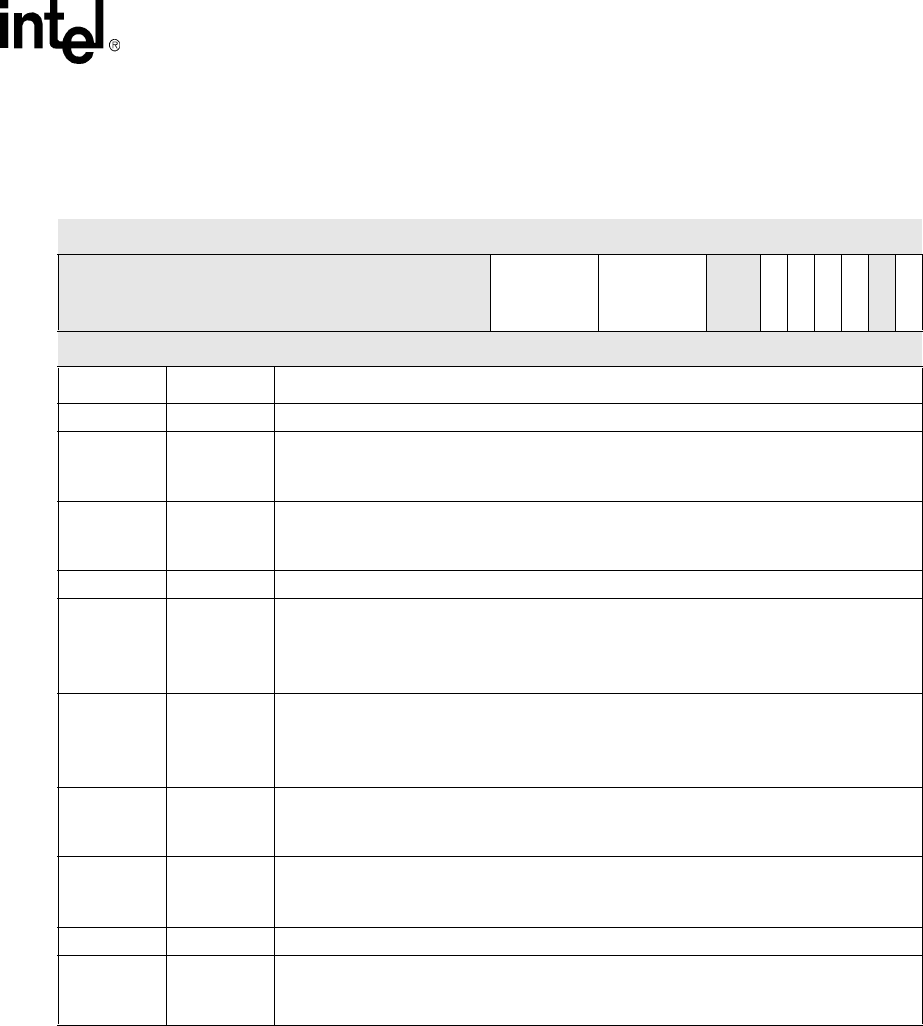

Table 14-3. SACR0 Bit Definitions

Physical Address

0x4040_0000

Serial Audio Controller Global

Control Register

I

2

S Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved RFTH TFTH

reserved

STRF

EFWR

RST

BCKD

reserved

ENB

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 0 1 1 1 0 0 0 0 0 0 0 0

Bits Name Description

31:16 — reserved

15:12 RFTH

Receive FIFO interrupt or DMA threshold. Set to value 0 – 15. This value must be set to the

threshold value minus 1.

Receive DMA Request asserted whenever the Receive FIFO has >= (RFTH+1) entries.

11:8 TFTH

Transmit FIFO interrupt or DMA threshold. Set to value 0 – 15. This value must be set to

the threshold value minus 1.

Transmit DMA Request asserted whenever the Transmit FIFO has < (TFTH+1) entries.

7:6 — reserved

5STRF

Select Transmit or Receive FIFO for EFWR based special purpose function:

0 = Transmit FIFO is selected

1 = Receive FIFO is selected

See Table 14-4 for details.

4EFWR

This bit enables a special purpose FIFO Write/Read function:

0 = Special purpose FIFO Write/Read Function is disabled

1 = Special purpose FIFO Write/Read Function is enabled

See Table 14-4 for details.

3RST

Resets FIFOs logic and all registers, except this register (SACR0):

0 = Not reset

1 = Reset is active to other registers

2BCKD

This bit specifies input/output direction of BITCLK:

0 = Input. BITCLK driven by an external source.

1 = Output. BITCLK generated internally and driven out to the CODEC.

1 — reserved

0ENB

Enable I

2

S function:

0 = I2SLINK is disabled

1 = I2SLINK is enabled