Intel® PXA255 Processor Developer’s Manual 13-13

AC’97 Controller Unit

The ACUNIT transmits the write to the Powerdown Register (0x26) over the AC-link. Set up the

ACUNIT so that it does not transmit data in Slots 3-12 when it writes 0x1000 to the PR4 bit of the

Powerdown Register. AC’97 revision 2.0 does not require the CODEC to process other data when

it receives a power down request. When the CODEC receives the power down request, it

immediately transitions BITCLK and SDATA_IN to a logic low level.

13.5.2 Waking up the AC-link

13.5.2.1 Wake up triggered by the CODEC

To wake up the AC-link, a CODEC drives SDATA_IN to a logic high level. The rising edge

triggers the Resume Interrupt if that CODEC’s resume enable bit is set to a one. The CPU then

wakes up the CODEC using the cold or warm reset sequence. The ACUNIT uses a warm reset to

wake up the primary CODEC. The CODEC detects a warm reset when SYNC is driven high for a

minimum of one microsecond and the BITCLK is absent. The CODEC must wait until it samples

SYNC low before it can start BITCLK. The CODEC that signaled the wake event must keep its

SDATA_IN high until it detects that a warm reset has been completed. The CODEC can then

transition its SDATA_IN low.

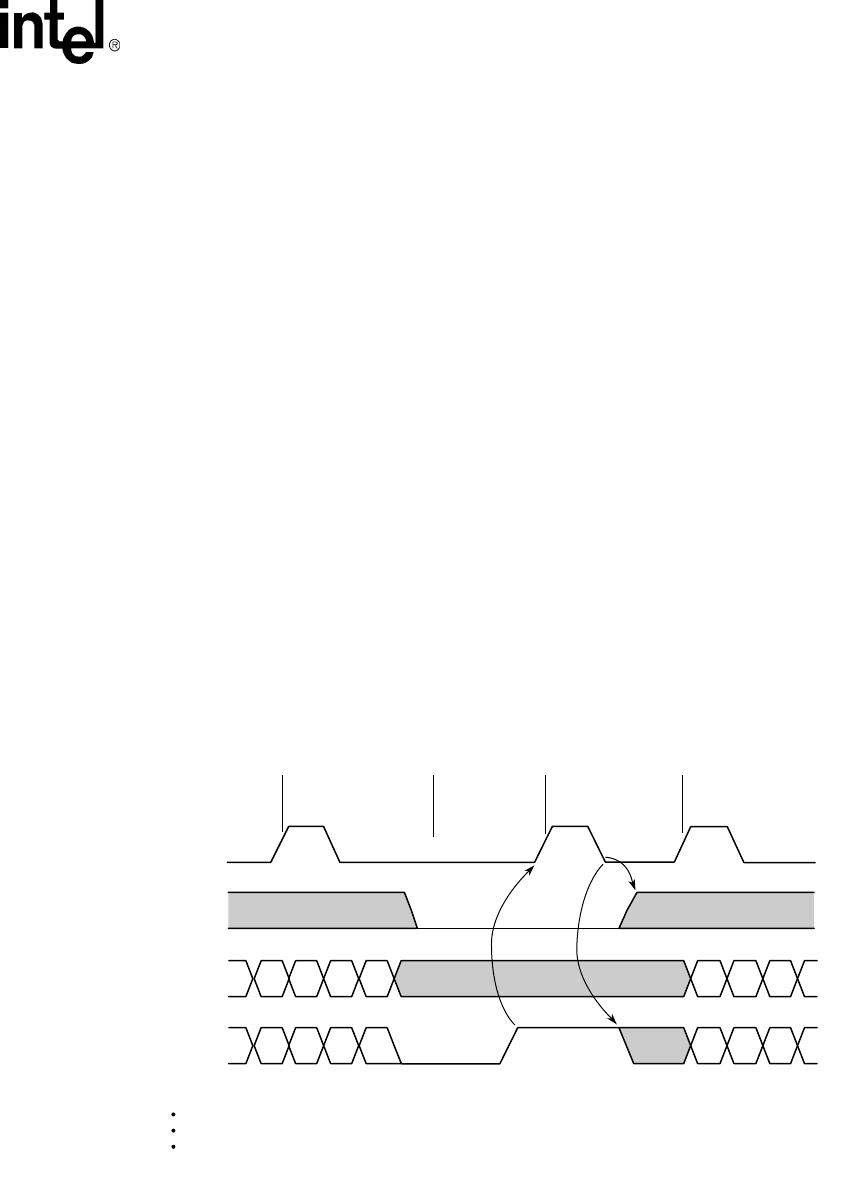

Figure 13-8 shows the AC-link timing for a wake up triggered by a CODEC. Because the processor

may need to be awakened, the Power Management unit detects the AC’97 wake-up event

(SDATA_IN high for more than one microsecond). When the ACUNIT is ready, it responds to the

wake-up event by asserting a warm or cold reset (see Figure 13-8). A Modem CODEC may require

the capacity to wake up the AC-link to report events such as Caller-ID and wake-up-on-ring.

Figure 13-8. SDATA_IN Wake Up Signaling

NOTES:

1. After SDATA_IN goes high, SYNC must be held for a minimum of 1 µSec.

2. The minimum SDATA_IN wake up pulse width is 1

µSec.

3. BITCLK not to scale

B1027-01

TAG

Note 1

Note 2

Notes:

After SDATA_IN goes high, SYNC must be held for a minimum of 1 µSec.

The minimum SDATA_IN wake up pulse width is 1 µSec.

BITCLK not to scale.

slot12

prev.

frame

slot12

prev.

frame

TAG

TAG

TAG

Slot

1

Slot

1

Slot

2

Slot

2

Write

to

0x26

Data

FR4

Power Down

Frame

Codec Sleep

State

Wake

Event

New Audio

Frame

SYNC

BITCLK

SDATA_OUT

SDATA_IN