2-16 Intel® PXA255 Processor Developer’s Manual

System Architecture

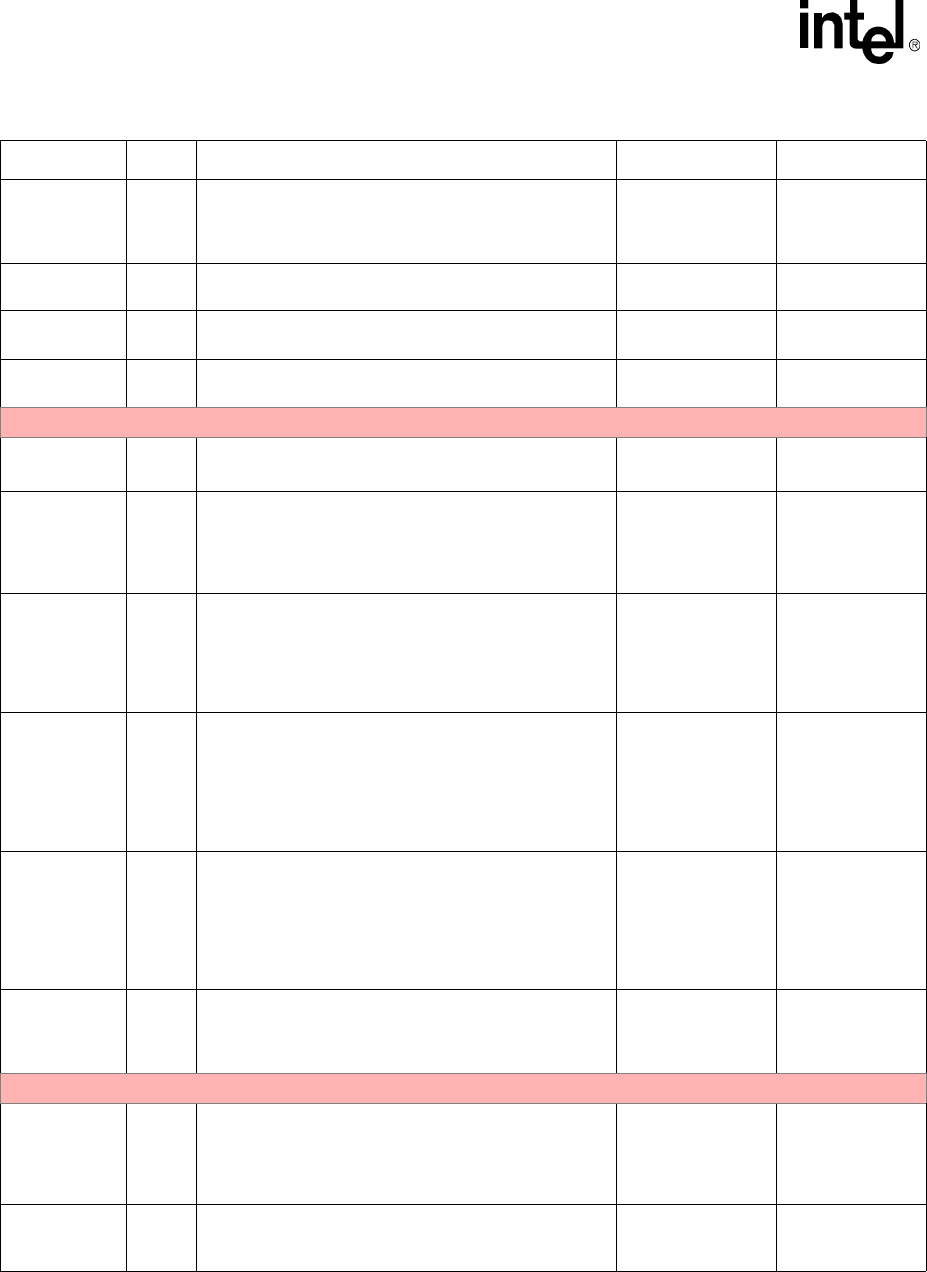

48MHz/GP[7] ICOCZ

48 MHz clock. (output) Peripheral clock output derived

from the PLL.

NOTE: This clock is only generated when the USB unit

clock enable is set.

Pulled High -

Note[1]

Note [3]

RTCCLK/

GP[10]

ICOCZ

Real time clock. (output) 1 Hz output derived from the

32kHz or 3.6864MHz output.

Pulled High -

Note[1]

Note [3]

3.6MHz/GP[11] ICOCZ

3.6864 MHz clock. (output) Output from 3.6864 MHz

oscillator.

Pulled High -

Note[1]

Note [3]

32kHz/GP[12] ICOCZ 32 kHz clock. (output) Output from the 32 kHz oscillator.

Pulled High -

Note[1]

Note [3]

Miscellaneous Pins

BOOT_SEL

[2:0]

IC Boot select pins. (input) Indicates type of boot device. Input Input

PWR_EN OC

Power Enable for the power supply. (output) When

negated, it signals the power supply to remove power to

the core because the system is entering sleep mode.

Driven High

Driven low while

entering sleep

mode. Driven high

when sleep exit

sequence begins.

nBATT_FAULT IC

Main Battery Fault. (input) Signals that main battery is

low or removed. Assertion causes PXA255 processor to

enter sleep mode or force an Imprecise Data Exception,

which cannot be masked. PXA255 processor will not

recognize a walk-up event while this signal is asserted.

Minimum assertion time for nBATT_FAULT is 1 ms.

Input Input

nVDD_FAULT IC

VDD Fault. (input) Signals that the main power source is

going out of regulation. nVDD_FAULT causes the

PXA255 processor to enter sleep mode or force an

Imprecise Data Exception, which cannot be masked.

nVDD_FAULT is ignored after a walk-up event until the

power supply timer completes (approximately 10 ms).

Minimum assertion time for nVDD_FAULT is 1 ms.

Input Input

nRESET IC

Hard reset. (input) Level sensitive input used to start the

processor from a known address. Assertion causes the

current instruction to terminate abnormally and causes a

reset. When nRESET is driven high, the processor starts

execution from address 0. nRESET must remain low until

the power supply is stable and the internal 3.6864 MHz

oscillator has stabilized.

Input

Input. Driving low

during sleep will

cause normal

reset sequence

and exit from sleep

mode.

nRESET_OUT OC

Reset Out. (output) Asserted when nRESET is asserted

and deasserts after nRESET is deasserted but before the

first instruction fetch. nRESET_OUT is also asserted for

“soft” reset events: sleep, watchdog reset, or GPIO reset.

Driven low during

any reset sequence

- driven high prior to

first fetch.

Driven Low

JTAG and Test Pins

nTRST IC

JTAG Test Interface Reset. Resets the JTAG/Debug

port. If JTAG/Debug is used, drive nTRST from low to

high either before or at the same time as nRESET. If

JTAG is not used, nTRST must be either tied to nRESET

or tied low.

Input Input

TDI IC

JTAG test data input. (input) Data from the JTAG

controller is sent to the PXA255 processor using this pin.

This pin has an internal pull-up resistor.

Input Input

Table 2-6. Pin & Signal Descriptions for the PXA255 Processor (Sheet 8 of 9)

Pin Name Type Signal Descriptions Reset State Sleep State