9-10 Intel® PXA255 Processor Developer’s Manual

I

2

C Bus Interface Unit

Arbitration can take a long time. If the address bit and the R/nW are the same, the arbitration

scheme considers the data. Because the I

2

C bus has a wired-AND nature, a transfer does not lose

data if multiple masters signal the same bus states. If the address and the R/nW bit or the data they

contain are different, the master signals a high state loses arbitration and shuts off its data drivers. If

the I

2

C unit loses arbitration, it shuts off the SDA or SCL drivers for the rest of the byte transfer,

sets the ISR[ALD] bit, and returns to slave-receive mode.

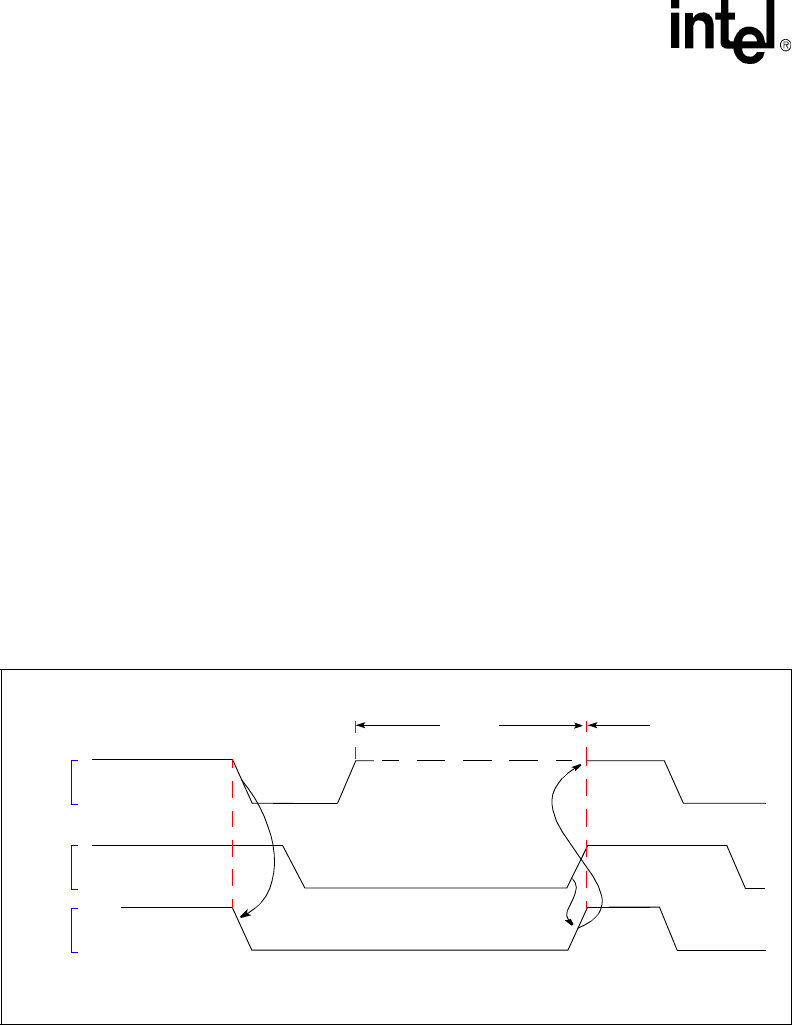

9.4.5.1 SCL Arbitration

Each master on the I

2

C bus generates its own clock on the SCL line for data transfers. As a result,

clocks with different frequencies may be connected to the SCL line. Because data is valid when a

clock is in the high period, bit-by-bit arbitration requires a defined clock synchronization

procedure.

Clock synchronization is through the wired-AND connection of the I

2

C interfaces to the SCL line.

When a master’s clock changes from high to low, the master holds down the SCL line for its

associated period (see Figure 9-6). A clock cannot switch from low to high if another master has

not completed its period. The master with the longest low period holds down the SCL line. Masters

with shorter periods are held in a high wait-state until the master with the longest period completes.

After the master with the longest period completes, the SCL line changes to the high state and

masters with the shorter periods continue the data cycle.

9.4.5.2 SDA Arbitration

Arbitration on the SDA line can continue for a long time because it starts with the address and R/

nW bits and continues through the data bits. Figure 9-7 shows the arbitration procedure for two

masters. More than two masters may be involved if more than two masters are connected to the

bus. If the address bit and the R/nW are the same, the arbitration scheme considers the data.

Because the I

2

C bus has a wired-AND nature, a transfer does not lose data if multiple masters

signal the same bus states. If the address and the R/nW bit or the data they contain are different, the

master that sent the first low data bit loses arbitration and shuts off its data drivers. If the I

2

C unit

loses arbitration, it shuts off the SDA or SCL drivers for the rest of the byte transfer, sets the

ISR[ALD] bit, and returns to slave-receive mode.

Figure 9-6. Clock Synchronization During the Arbitration Procedure

CLK2

SCL

Wait

State

Start Counting

High Period

CLK1

The first master to complete its high

period pulls the SCL line low.

The master with the longest clock

period holds the SCL line low.