Intel® PXA255 Processor Developer’s Manual 3-39

Clocks and Power Manager

3.7.1 Core Clock Configuration Register (CCLKCFG)

The CCLKCFG register (CP14 register 6), shown in Table 3-24, is used to enter the turbo mode

and frequency change sequence. To enter the mode or sequence, software executes the appropriate

function from Table 3-23. All core-initiated memory requests are completed before the Clocks and

Power Manager initiates the desired mode or sequence.

To ensure that CCLKCFG[TURBO] does not change when entering the frequency change

sequence, software must do a read-modify-write.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

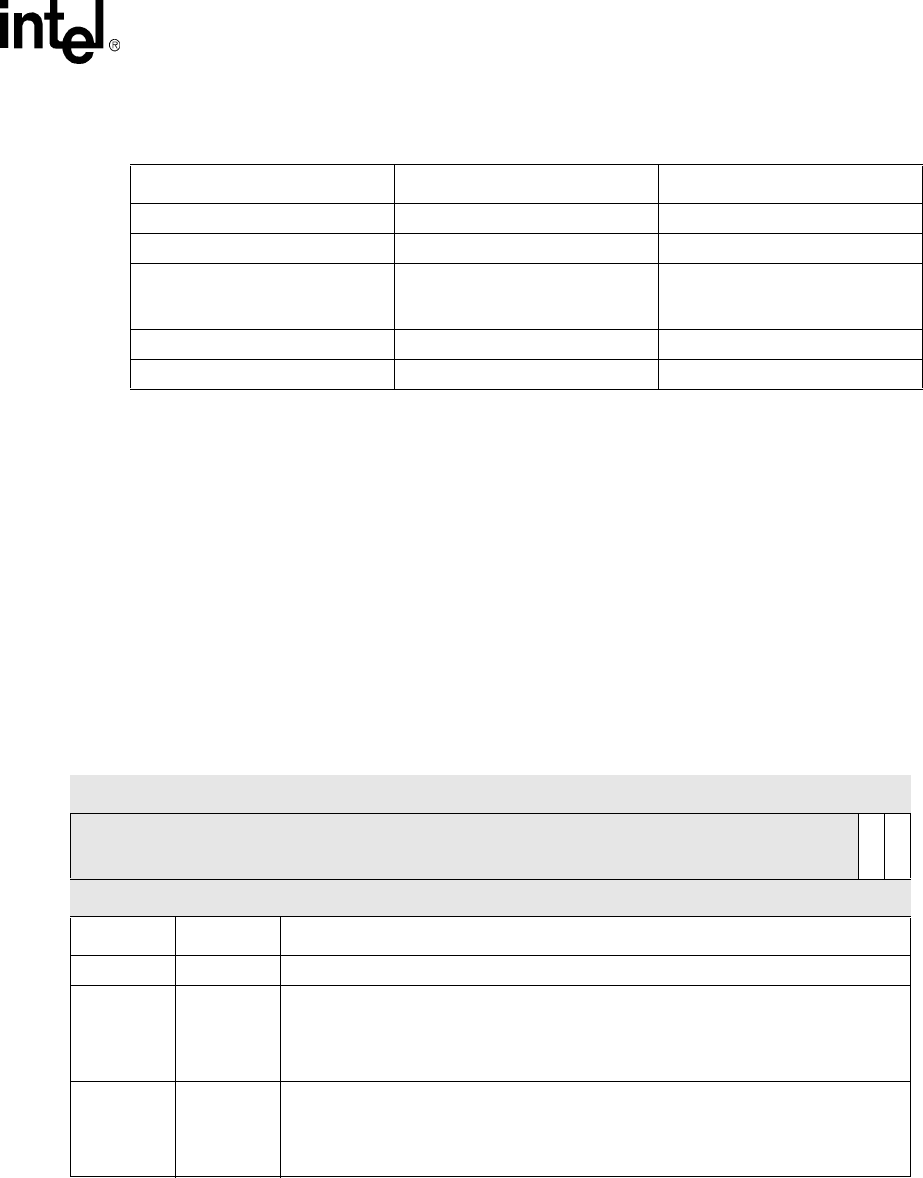

Table 3-23. Coprocessor 14 Clock and Power Management Summary

Function Data in Rd Instruction

Read CCLKCFG — MRC p14, 0, Rd, c6, c0, 0

Enter turbo mode TURBO = 1 MCR p14, 0, Rd, c6, c0, 0

Enter frequency change sequence

FCS = 1

(Turbo mode bit may be set or

cleared in the same write)

MCR p14, 0, Rd, c6, c0, 0

Enter idle mode M = 1 MCR p14, 0, Rd, c7, c0, 0

Enter sleep mode M = 3 MCR p14, 0, Rd, c7, c0, 0

Table 3-24. CCLKCFG Bit Definitions

CP14

Register 6

CCLKCFG Clocks and Power Manager

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

FCS

TURBO

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

[31:2] — reserved

1FCS

Frequency Change Sequence

0 – Do not enter frequency change sequence

1 – Enter frequency change sequence

Cleared on hardware, watchdog, and GPIO reset and when sleep mode exits.

0TURBO

Turbo Mode

0 – Do not enter turbo mode/Exit turbo mode

1 – Enter turbo mode

Cleared on hardware, watchdog, and GPIO reset and when sleep mode exits.