Intel® PXA255 Processor Developer’s Manual 4-45

System Integration Unit

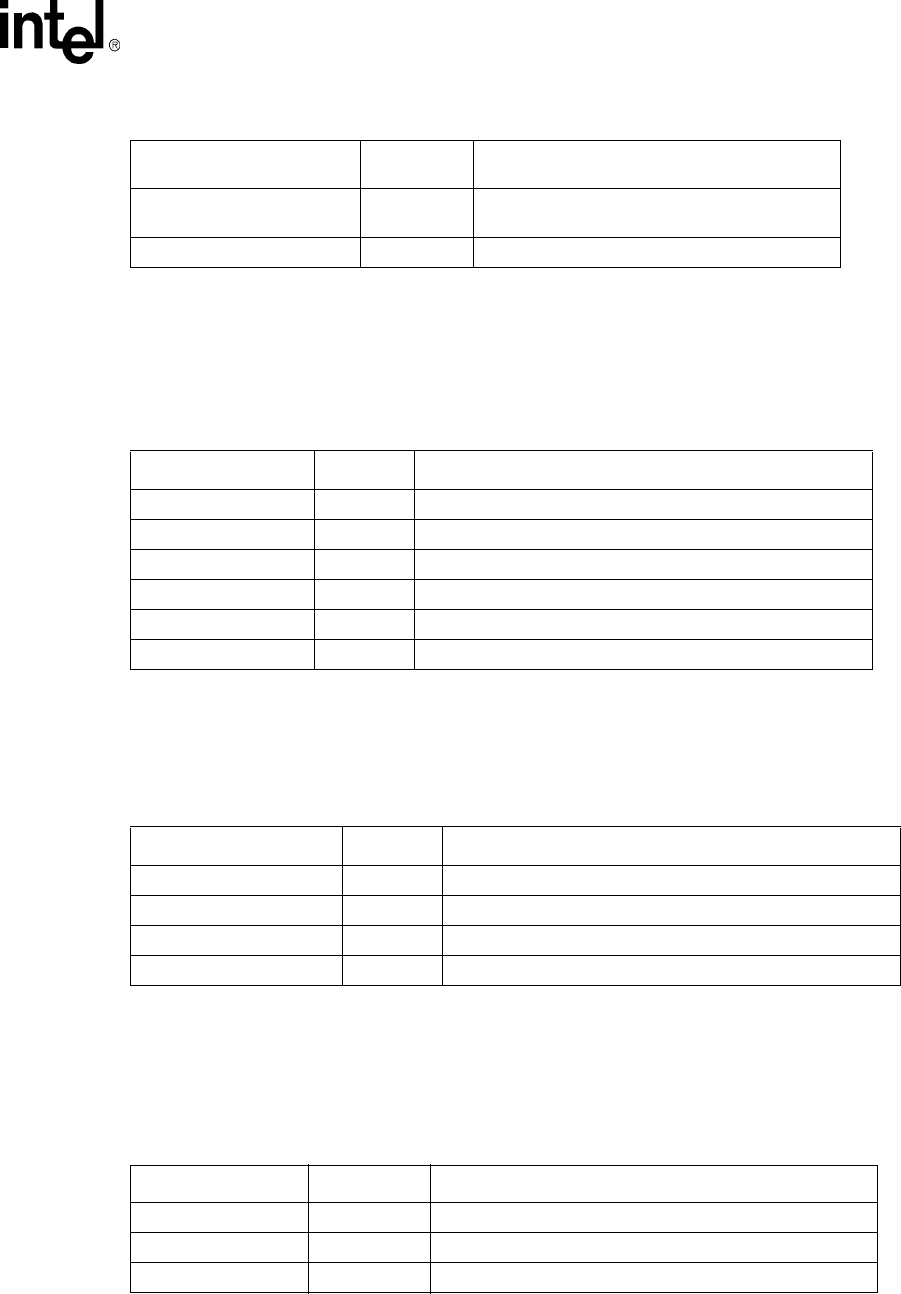

4.6.2 Interrupt Controller Register Locations

Table 4-50 shows the registers associated with the interrupt controller block and their physical

addresses.

4.6.3 Real-Time Clock Register Locations

Table 4-51 describes the location of the RTC registers.

4.6.4 OS Timer Register Locations

Table 4-52 shows the registers associated with the OS timer and the physical addresses used to

access them.

0x40E0_0060 GAFR1_U

GPIO alternate function select register

GPIO[63:48]

0x40E0_0064 GAFR2_L

GPIO alternate function select register

GPIO[79:64]

0x40E0_0068 GAFR2_U GPIO alternate function select register GPIO[80]

Table 4-49. GPIO Register Addresses (Sheet 2 of 2)

Table 4-50. Interrupt Controller Register Addresses

Address Name Description

0x40D0_0000 ICIP Interrupt controller IRQ pending register

0x40D0_0004 ICMR Interrupt controller mask register

0x40D0_0008 ICLR Interrupt controller level register

0x40D0_000C ICFP Interrupt controller FIQ pending register

0x40D0_0010 ICPR Interrupt controller pending register

0x40D0_0014 ICCR Interrupt controller control register

Table 4-51. RTC Register Addresses

Address Name Description

0x4090_0000 RCNR RTC count register

0x4090_0004 RTAR RTC alarm register

0x4090_0008 RTSR RTC status register

0x4090_000C RTTR RTC trim register

Table 4-52. OS Timer Register Addresses (Sheet 1 of 2)

Address Name Description

0x40A0_0000 OSMR0 OS timer match register 0

0x40A0_0004 OSMR1 OS timer match register 1

0x40A0_0008 OSMR2 OS timer match register 2