Intel® PXA255 Processor Developer’s Manual 8-17

Synchronous Serial Port Controller

8.7.4.1 Transmit FIFO Not Full Flag (TNF)

This non-interruptible bit is set whenever the transmit FIFO is not full. TNF is cleared when the

FIFO is completely full. This bit can be polled when using programmed I/O to fill the transmit

FIFO over its threshold level. This bit does not request an interrupt.

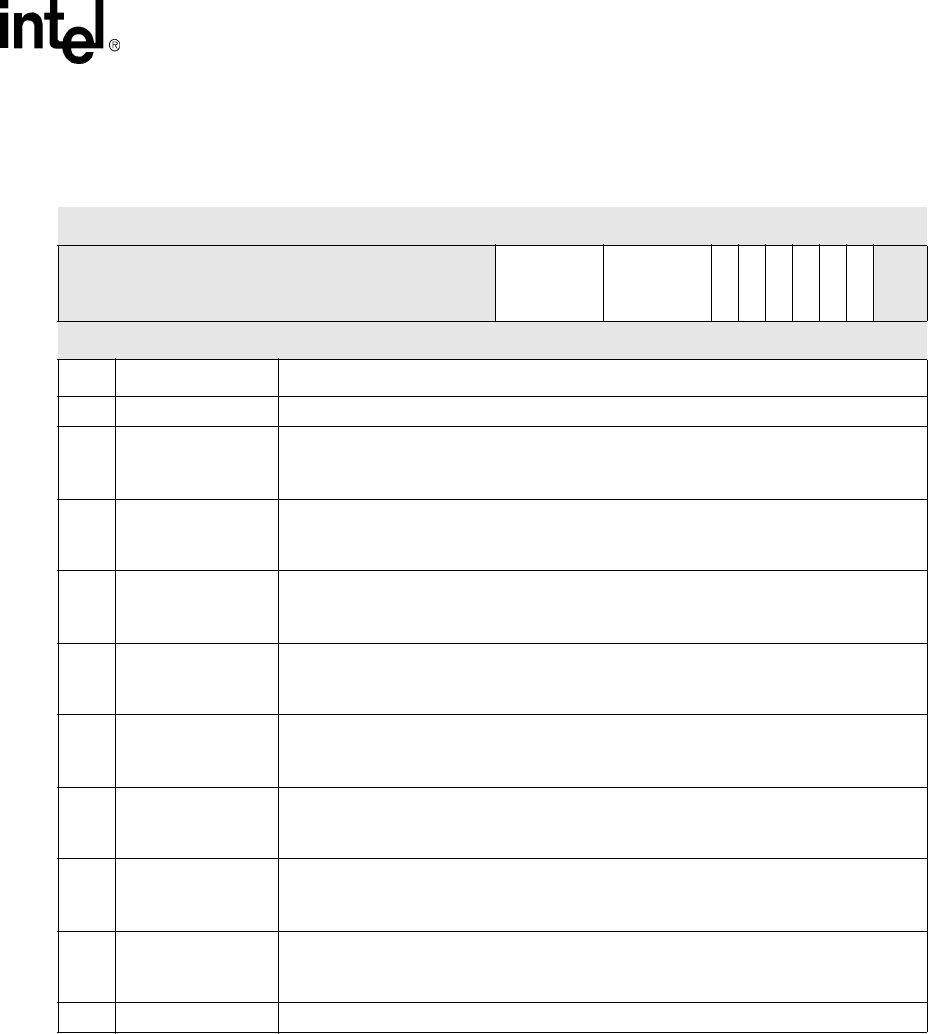

Table 8-6. SSSR Bit Definitions

0x4100_0008 SSP Status Register (SSSR) Synchronous Serial Port Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved RFL TFL

ROR

RFS

TFS

BSY

RNE

TNF

reserved

Reset X 0xF 0x0 0 0 0 0 0 1 0

Bits Name Description

1:0 — reserved

2TNF

Transmit FIFO Not Full (read only)

0 = Transmit FIFO is full

1 = Transmit FIFO is not full

3RNE

Receive FIFO Not Empty (read only)

0 = Receive FIFO is empty

1 = Receive FIFO is not empty

4BSY

SSP Busy (read only)

0 = SSP is idle or disabled

1 = SSP currently transmitting or receiving a frame

5TFS

Transmit FIFO Service Request (read only)

0 = Transmit FIFO level exceeds TFT threshold, or SSP disabled

1 = Transmit FIFO level is at or below TFT threshold, generate interrupt or DMA request

6RFS

Receive FIFO Service Request (read only)

0 = Receive FIFO level exceeds RFT threshold, or SSP disabled

1 = Receive FIFO level is at or above RFT threshold, generate interrupt or DMA request

7ROR

Receive FIFO Overrun (read/write)

0 = Receive FIFO has not experienced an overrun

1 = Attempted data write to full Receive FIFO, request interrupt

11:8 TFL

Transmit FIFO Level (read only)

Number of entries in Transmit FIFO. Note: When the value 0x0 is read, the FIFO is either

empty or full and the software must refer to the TNF bit.

15:12 RFL

Receive FIFO Level (read only)

Number of entries minus one in Receive FIFO. Note: When the value 0xF is read, the FIFO

is either empty or full and the software must refer to the RNE bit.

31:16 — reserved