Intel® PXA255 Processor Developer’s Manual 5-13

DMA Controller

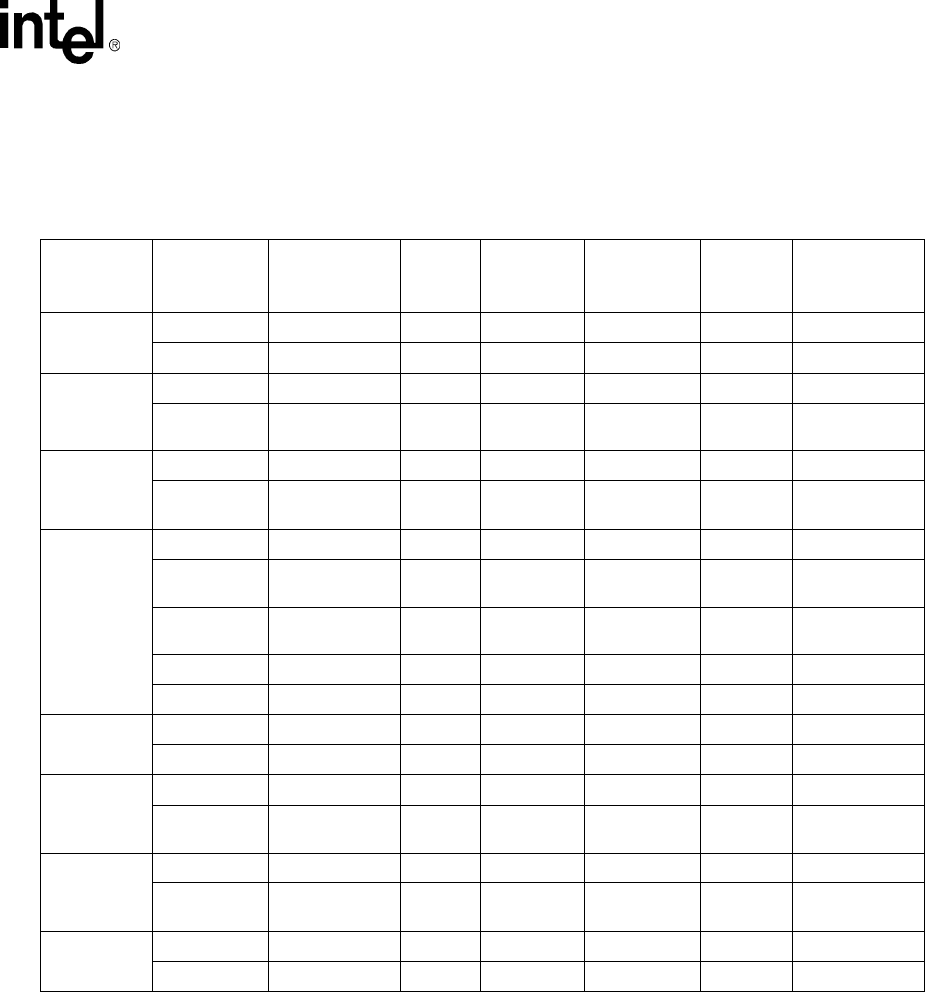

5.2.2 Quick Reference for DMA Programming

Use Table 5-5 as a quick reference sheet for programming the DMA.

Table 5-5. DMA Quick Reference for Internal Peripherals (Sheet 1 of 2)

Unit Function FIFO Address

Width

(bytes)

DCMD.

Width

(binary)

Burst Size

(bytes)

Source

or

Target

DRCMR

I2S

receive 0x4040_0080 4 11 8, 16, 32 Source 0x4000_0108

transmit 0x4040_0080 4 11 8, 16, 32 Target 0x4000_010c

BTUART

receive 0x4020_0000 1 01 8, 16, 32 Source 0x4000_0110

transmit 0x4020_0000 1 01

8, 16, 32 or

trailing

Target 0x4000_0114

FFUART

receive 0x4010_0000 1 01 8, 16, 32 Source 0x4000_0118

transmit 0x4010_0000 1 01

8, 16, 32 or

trailing

Target 0x4000_011c

AC97

microphone 0x4050_0060 4 11 8, 16, 32 Source 0x4000_0120

modem

receive

0x4050_0140 4 11 8, 16, 32 Source 0x4000_0124

modem

transmit

0x4050_0140 4 11 8, 16, 32 Target 0x4000_0128

audio receive 0x4050_0040 4 11 8, 16, 32 Source 0x4000_012c

audio transmit 0x4050_0040 4 11 8, 16, 32 Target 0x4000_0130

SSP

receive 0x4100_0010 2 10 8, 16 Source 0x4000_0134

transmit 0x4100_0010 2 10 8, 16 Target 0x4000_0138

FICP

receive 0x4080_000C 1 01 8, 16, 32 Source 0x4000_0144

transmit 0x4080_000C 1 01

8, 16, 32 or

trailing

Target 0x4000_0148

STUART

receive 0x4070_0000 1 01 8, 16, 32 Source 0x4000_014c

transmit 0x4070_0000 1 01

8, 16, 32, or

trailing

Target 0x4000_0150

MMC

receive 0x4110_0040 1 01 32 or trailing Source 0x4000_0154

transmit 0x4110_0044 1 01 32 or trailing Target 0x4000_0158