Intel® PXA255 Processor Developer’s Manual 17-11

Hardware UART

Load these divisor latches during initialization to ensure that the baud rate generator operates

properly. If each divisor latch is loaded with a 0, the 16X clock stops. The divisor latches are

accessed with a word write.

The baud rate of the data shifted in to or out of a UART is given by the formula:

For example, if the divisor is 24, the baud rate is 38400 bps.

The divisor’s reset value is 0x0002.

Table 17-4 and Table 17-5 describe the DLL and DLH registers.

These are read/write registers. Ignore reads from reserved bits. Write zeros to reserved bits.

17.5.4 Interrupt Enable Register (IER)

The IER, shown in Table 17-6, enables the five types of interrupts that set a value in the Interrupt

Identification register (IIR) (refer to Section 17.5.5). To disable an interrupt, software must clear

the appropriate bit in the IER. Software can enable some interrupts by setting the appropriate bit.

The character timeout indication interrupt is separated from the received data available interrupt to

ensure that the processor and the DMA controller do not service the receive FIFO at the same time.

When a character timeout indication interrupt occurs, the processor must handle the data in the

receive FIFO through programmed I/O.

BaudRate

14.7456 MHz

16xDivisor()

----------------------------------=

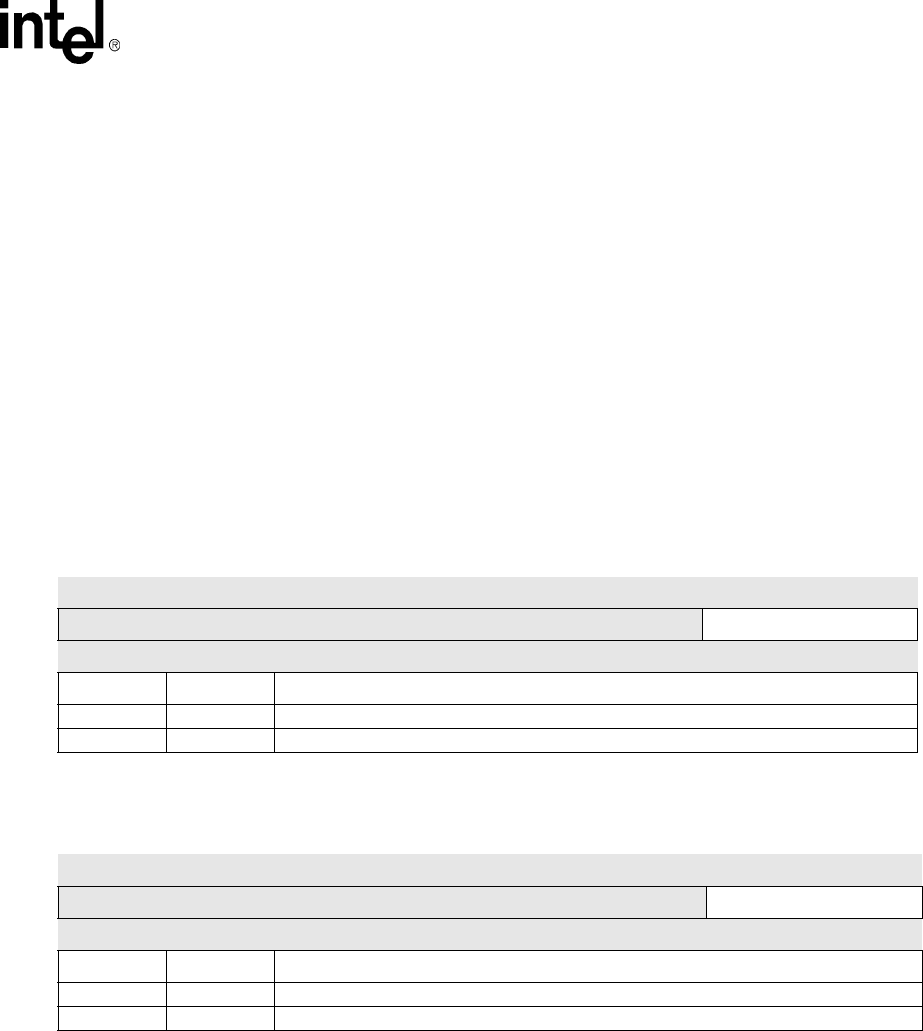

Table 17-4. DLL Bit Definitions

Physical Address

0x4160_0000 (DLAB=1)

Divisor Latch Register Low (DLL) PXA255 Processor Hardware UART

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved DLL

Reset

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 0 0 0 0 0 0 1 0

Bits Name Description

31:8 — reserved

7:0 DLL Low byte compare value to generate baud rate

Table 17-5. Divisor Latch Register High (DLH) Bit Definitions

Physical Address

0x4160_0004 (DLAB=1)

Divisor Latch Register High (DLH) PXA255 Processor Hardware UART

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved DLH

Reset

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 0 0 0 0 0 0 0 0

Bits Name Description

31:8 — reserved

7:0 DLH High byte compare value to generate baud rate