6-14 Intel® PXA255 Processor Developer’s Manual

Memory Controller

6.5.3 SDRAM MDREFR Register (MDREFR)

MDREFR, shown in Table 6-5, is a read/write register and contains control bits that refresh both

SDRAM partition pairs. MDREFR also contains control and status bits for SDRAM self-refresh,

SDRAM/SMROM clock divisors, SDRAM/SMROM clocks running, and SDRAM/SMROM

clock-enable pin states. Independent control/status is provided for each of the clock pins

(SDCLK[2:0]) and clock-enable pins (SDCKE[1:0]).

The clock-run bits (K0RUN, K1RUN, and K2RUN) and clock-enable bits (E0PIN and E1PIN)

provide software control of SDRAM and Synchronous Static Memory low-power modes. When

the clock-run bits and clock-enable bits are cleared, the corresponding memory is inaccessible.

Automatic power-down, enabled by the APD bit, is an mechanism for minimizing power

consumption in the processor SDCLK pin drivers and/or the SDRAM/Synchronous Static Memory

devices. A latency penalty of one memory cycle is incurred when SDCLK and SDCKE are

restarted between non-consecutive SDRAM/Synchronous Static Memory transfers.

The following conditions determine whether SDRAM refreshes occur.

• No refreshes are sent to SDRAM when the refresh counter is cleared to zero.

• If a single transaction to a disabled SDRAM partition is requested, a refresh to all four

partitions is performed.

• If all four SDRAM partitions are disabled, the refresh counter is disabled.

• If the clock frequency is changed, the register must be rewritten, even if the value has not

changed. This results in a refresh and the refresh counter being reset to the next refresh

interval.

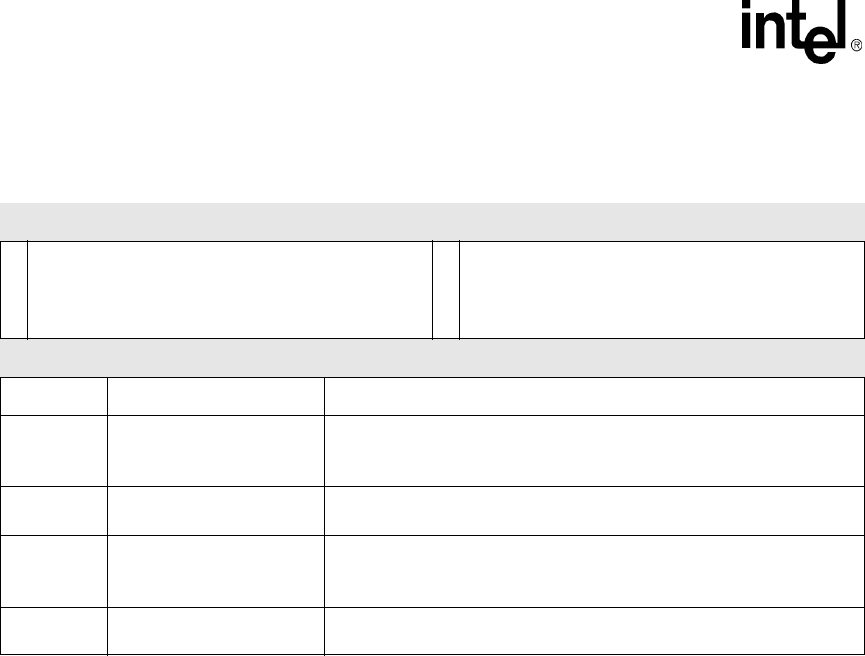

Table 6-4. MDMRSLP Register Bit Definitions

0X4800 0058 MDMRSLP

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

MDLPEN2

MDMRSLP2

MDLPEN0

MDMRSLP0

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

31 MDLPEN2

ENABLE BIT FOR LOW POWER MRS VALUE FOR PARTITION PAIR 2/3:

0 – Disable low power MRS for Partition Pair 2/3

1 – Enable low power MRS for Partition Pair 2/3

30:16 MDMRSLP2

LOW POWER MRS VALUE TO BE WRITTEN TO SDRAM FOR

PARTITION PAIR 2/3

15 MDLPEN0

Enable bit for low power MRS value for Partition Pair 0/1.

0 – Disable low power MRS for Partition Pair 0/1

1 – Enable low power MRS for Partition Pair 0/1

14:0 MDMRSLP0

LOW POWER MRS VALUE TO BE WRITTEN TO SDRAM FOR

PARTITION PAIR 0/1