Intel® PXA255 Processor Developer’s Manual 12-25

USB Device Controller

SET_CONFIGURAION and SET_INTERFACE command with a NAK until AREN is set to 1.

When the user sets AREN to 1, the UDC responds with an ACK to the next STATUS IN request.

AREN is cleared by the UDC when another SETUP command is received.

12.6.3 UDC Endpoint 0 Control/Status Register (UDCCS0)

UDCCS0, shown in Table 12-14, contains seven bits that are used to operate endpoint zero, the

control endpoint.

12.6.3.1 OUT Packet Ready (OPR)

The OUT packet ready bit is set by the UDC when it receives a valid OUT packet to endpoint zero.

When this bit is set, the USIR0[IR0] bit will be set in the UDC status/interrupt register if endpoint

zero interrupts are enabled. This bit is cleared by writing a one. The UDC is not allowed to enter

the data phase of a transaction until this bit is cleared.

12.6.3.2 IN Packet Ready (IPR)

The IN packet ready bit is set by the core if less than max_packet bytes (16) have been written to

the endpoint 0 FIFO to be transmitted. The core must not set this bit if a max_packet is to be

transmitted. The UDC clears this bit when the packet has been successfully transmitted, the

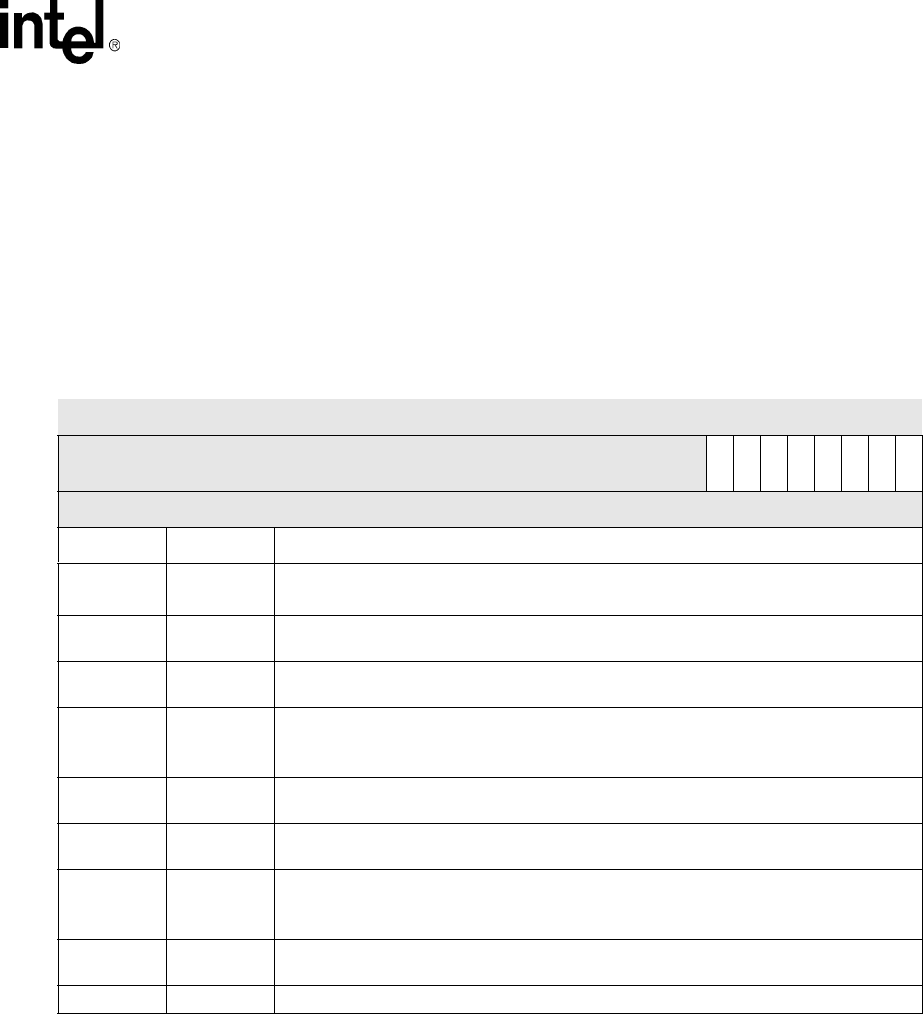

Table 12-14. UDCCS0 Bit Definitions

0x 4060_0010 UDCCS0 USB Device Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

SA

RNE

FST

SST

DRWF

FTF

IPR

OPR

x x x x x x x x x x x x x x x x x x x x x x x x 0 0 0 0 0 0 0 0

Bits Name Description

0OPR

OUT packet ready (read/write 1 to clear)

1 = OUT packet ready.

1IPR

IN packet ready (always read 0/write 1 to set).

1 = IN packet ready.

2 FTF

Flush Tx FIFO (always read 0/write 1 to set)

1 = Flush the contents of Tx FIFO.

3 DRWF

Device remote wakeup feature (read-only)

0 = Device Remote Wakeup Feature is disabled.

1 = Device Remote Wakeup Feature is enabled.

4SST

Sent stall (read/write 1 to clear).

1 = UDC sent stall handshake

5FST

Force stall (read/write 1 to set).

1 = Force stall handshake

6RNE

Receive FIFO not empty (read-only).

0 = Receive FIFO empty.

1 = Receive FIFO not empty.

7SA

Setup Active (read/write 1 to clear)

1 = Setup command is active on the USB

31:8 — reserved