9-14 Intel® PXA255 Processor Developer’s Manual

I

2

C Bus Interface Unit

.

\

9.4.7 Slave Operations

Table 9-6 describes how the I

2

C unit operates as a slave device.

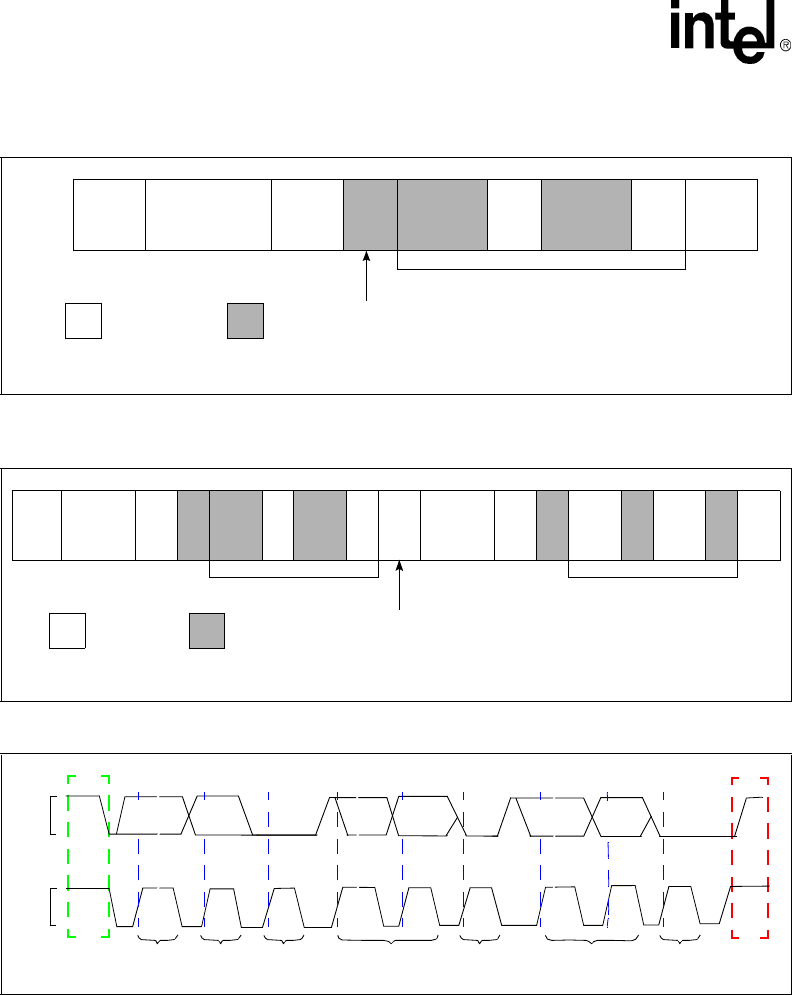

Figure 9-8. Master-Receiver Read from Slave-Transmitter

Figure 9-9. Master-Receiver Read from Slave-Transmitter / Repeated Start / Master-

Transmitter Write to Slave-Receiver

Figure 9-10. A Complete Data Transfer

Master to Slave

Slave to Master

START

Slave Address

R/nW

1

ACK

Data

Byte

ACK

Data

Byte

STOP

N Bytes + ACK

ACK

Default

Slave-Receive

Mode

First Byte Read

START

Slave

R/nW

1

ACK

Data

Byte

ACK

Data

Byte

N Bytes + ACK

Read

ACK Sr

Slave

R/nW

0

ACK

Data

Byte

ACK

Data

Byte

STOP

N Bytes + ACK

Write

ACK

Address Address

Master to Slave Slave to Master

Repeated

Start

Data Chaining

SDA

SCL

Start

Condition

Address

R/nW

ACK

Data

ACK Data

1-7 8 9 8 989

1-7 1-7

ACK

Stop

Condition

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼