Intel® PXA255 Processor Developer’s Manual 9-23

I

2

C Bus Interface Unit

on the acknowledge pulse in receiver mode. After the processor reads the IDBR, the ACK/NAK

Control bit is written and the Transfer Byte bit is written, allowing the next byte transfer to proceed

to the I

2

C bus. The IDBR register is 0x00 after reset.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

9.9.3 I

2

C Control Register (ICR)

The processor uses the ICR, shown in Table 9-10, to control the I

2

C unit.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

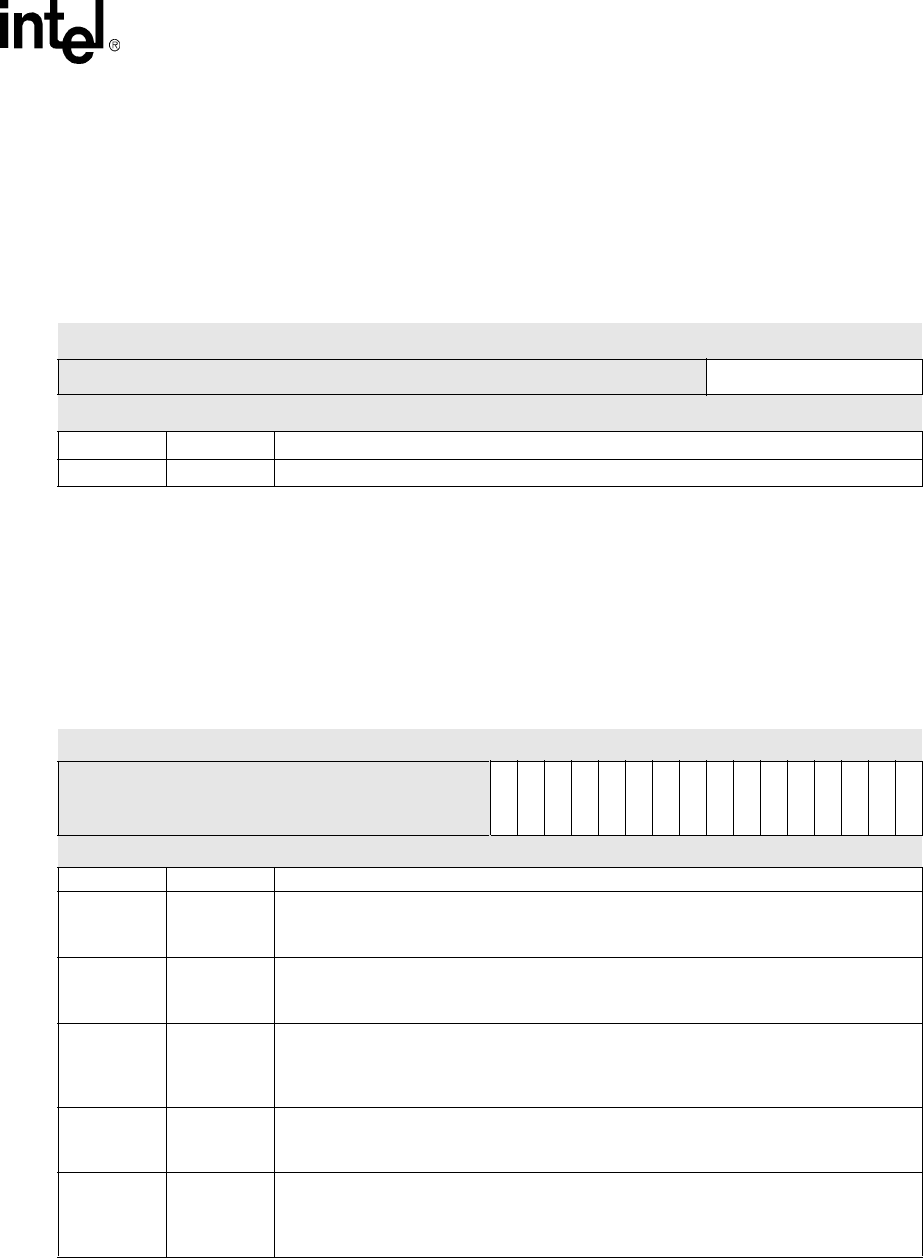

Table 9-9. IDBR Bit Definitions

Physical Address

4030_1688

I

2

C Data Buffer Register I

2

C Bus Interface Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved IDB

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

31:8 — reserved

7:0 IDB I

2

C Data Buffer: Buffer for I

2

C bus send/receive data.

Table 9-10. ICR Bit Definitions (Sheet 1 of 3)

Physical Address

4030_1690

I

2

C Control Register I

2

C Bus Interface Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

FM

UR

SADIE

ALDIE

SSDIE

BEIE

IRFIE

ITEIE

GCD

IUE

SCLE

MA

TB

ACKNAK

STOP

START

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

31:16 — reserved

15 FM

Fast Mode:

0 = 100 KBit/sec. operation

1 = 400 KBit/sec. operation

14 UR

Unit Reset:

0 = No reset.

1 = Reset the I

2

C unit only.

13 SADIE

Slave Address Detected Interrupt Enable:

0 = Disable interrupt.

1 = Enables the I

2

C unit to interrupt the processor when it detects a slave address match or

general call address.

12 ALDIE

Arbitration Loss Detected Interrupt Enable:

0 = Disable interrupt.

1 = Enables the I

2

C unit to interrupt the processor when it loses arbitration in master mode.

11 SSDIE

Slave STOP Detected Interrupt Enable:

0 = Disable interrupt.

1 = Enables the I

2

C unit to interrupt the processor when it detects a STOP condition in

slave mode.