12-24 Intel® PXA255 Processor Developer’s Manual

USB Device Controller

12.6.2 UDC Control Function Register (UDCCFR)

The UDC Control Function register (UDCCFR) contains 1 mode bit and 1 enable bit that lets

software delay sending back an ACK response to SET_CONFIG or SET_INTERFACE commands

from the host. The remaining bits are reserved.

12.6.2.1 ACK Control Mode

The ACK control mode (ACM) bit enables user control of the ACK response to the status IN

requests of SET_CONFIGURATION and SET_INTERFACE commands. When ACM is set to 0,

the UDC automatically responds to the STATUS IN request following a SET_CONFIGURATION

and SET_INTERFACE with an ACK. When ACM is set to 1, the UDC responds to the STATUS

IN request following a SET_CONFIGURATION and SET_INTERFACE command with a NAK

until AREN is set to 1. When the user sets AREN to 1, the UDC responds with an ACK to the next

STATUS IN request.

12.6.2.2 ACK Response Enable

When ACM = 1, the ACK response enable (AREN) bit enables user control of the ACK response

to the status IN requests of SET_CONFIGURATION and SET_INTERFACE commands. When

ACM is set to 1, the UDC responds to the STATUS IN request following a

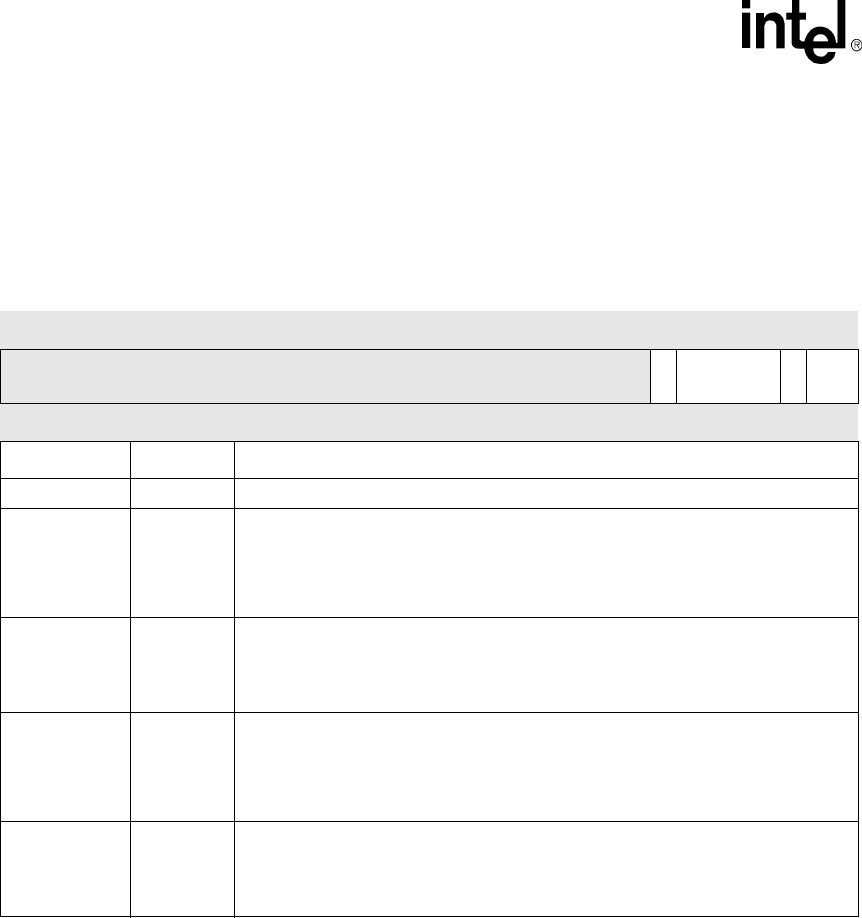

Table 12-13. UDC Control Function Register

0x 4060_0008 UDCCFR USB Device Controller

Bit

32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

AREN

MB1

ACM

MB1

Reset X X X X X X X X X X X X X X X X X X X X X X X X X 1 1 1 1 1 1 1 1

Bits Name Description

31:8 — Reserved – Read as unknown and must be written as zero.

7AREN

ACK RESPONSE ENABLE (read/write 1 to set)

0 = Send NAK response to SET_CONFIGURATION and SET_INTERFACE

commands

1 = Send ACK response to SET_CONFIGURATION and SET_INTERFACE

commands

6:2 MB1

MB1

This bit must be set to 1.

0 = Reserved

1 = Must be configured to 1.

2ACM

ACK CONTROL MODE (read/write 1 to set)

0 = Send ACK response to SET_CONFIGURATION and SET_INTERFACE

commands with no user intervention (B-step default)

1 = Send NAK response to SET_CONFIGURATION and SET_INTERFACE

commands until UDCCFR[AREN] = 1

1MB1

MB1

This bit must be set to 1.

0 = Reserved

1 = Must be configured to 1.