DEFINITY Enterprise Communications Server Release 7

Maintenance for R7r

555-230-126

Issue 4

June 1999

Maintenance Object Repair Procedures

9-1343PROCR (RISC Processor Circuit Pack)

9

PROCR (RISC Processor Circuit Pack)

The UN331B Processor circuit pack executes the system software, including all

call processing, maintenance and administration functions. The Processor circuit

pack is the most critical component for correct system operation.

Full system operation depends on nearly every circuit pack in the SPE. However,

the ability to load and run the maintenance software by the Processor circuit

pack depends only on correct Memory, Processor Bus, Tape-Disk-MSSNET and

SYSAM operation.

There are many Processor circuit pack problems (or other SPE problems) that will

result in the SPE being unable to load or run software. This condition is indicated

by the message "SPE Down" displayed on the terminal. In these cases, refer to

the SPE DOWN section of this manual for repair procedures.

The Processor circuit pack contains an instruction cache and a data cache.

These caches provide local, high speed memory that is closely coupled with the

processing function on the Processor circuit pack. The local nature of the caches

speeds up system operation by eliminating many external Memory accesses

when reading instructions or data. As the Processor runs, it tries to use

information already in the cache so that time will not be wasted going out to

memory. If it does not find the information in the cache, it reads it from memory

and stores it in the cache for possible future use. Over time, most instruction or

data accesses are likely to be satisfied by current information in the cache.

Problems in the cache circuits may stop the Processor from running or may only

result in reduced system performance.

The Processor circuit pack contains a Burst Read function that transfers multiple

words of instructions from memory with each request. This is done to speed up

the transfer of information from the Memory to the Processor, and is especially

helpful for "filling up" the cache in parallel with internal processing on Processor

circuit pack. Most of the circuitry needed to support this function is found on the

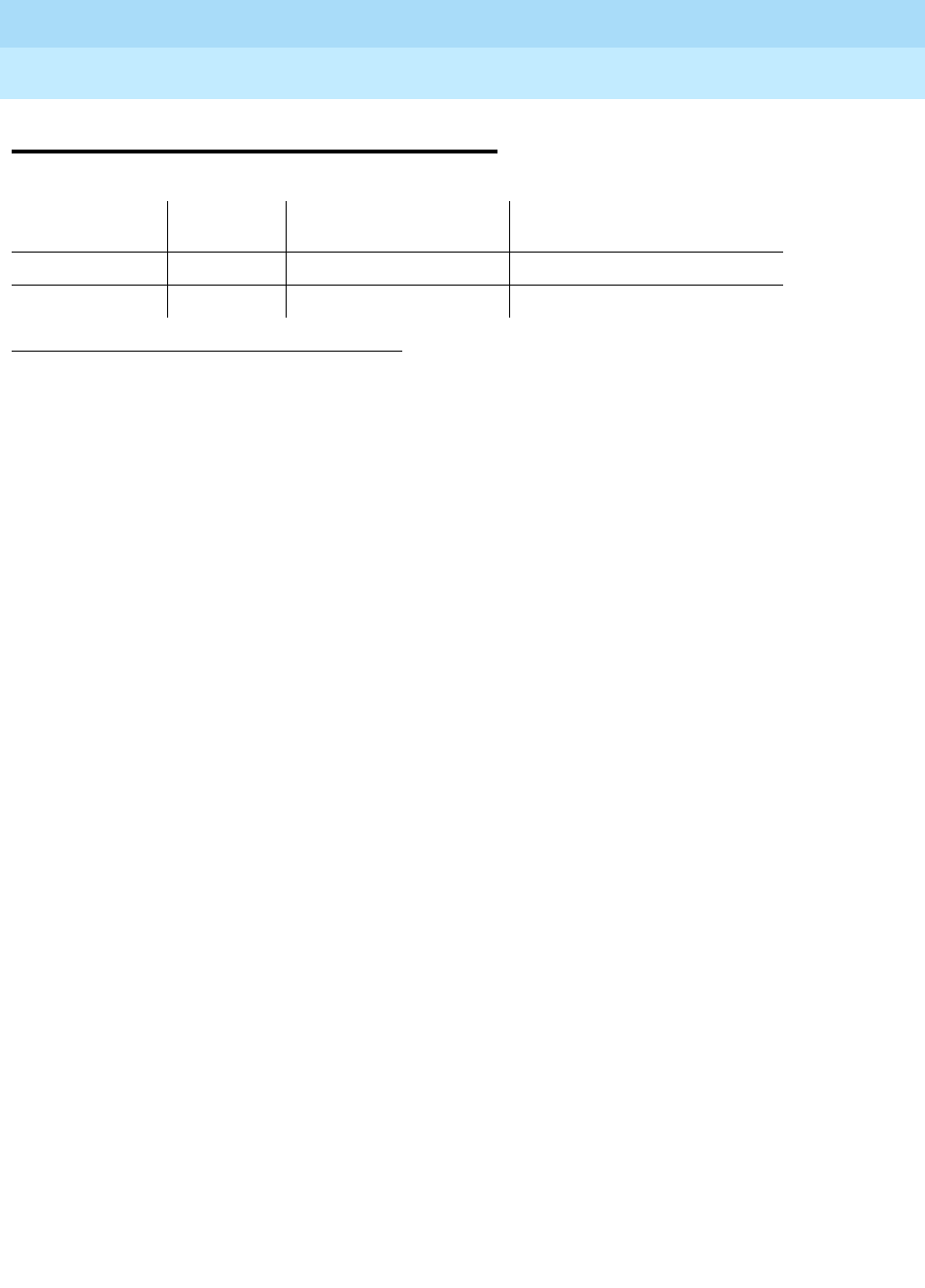

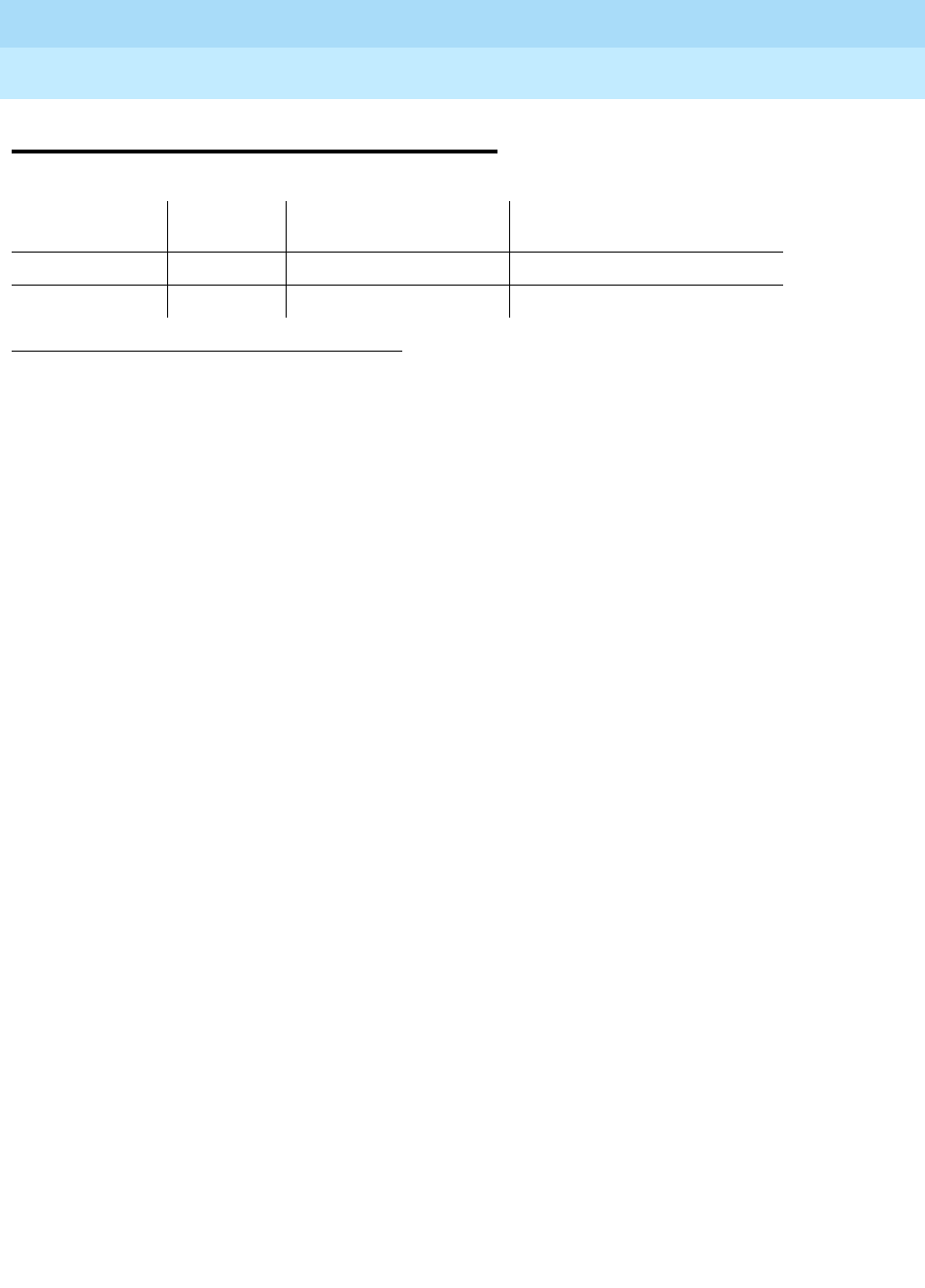

MO Name (in

Alarm Log)

Alarm

Level

Initial Command to

Run

1

1. UU is the cabinet number (always 1, not required). With simplex SPE, carrier designation is not

required. With duplicated SPEs, carrier a or b must be specified.

Full Name of MO

PROCR MAJOR

2

2. After a spontaneous SPE interchange has occurred, the Alarm Log retains for three hours a

record of any MAJOR ON-BOARD alarm against an SPE component that took place before the

interchange. If a spontaneous interchange has occurred (as indicated by STBY-SPE error type

103 or the display initcauses screen), and handshake is down, (check with status spe),

replace the alarmed circuit pack on the standby SPE. If handshake is up, execute a test long

clear of the alarmed circuit pack and follow recommended procedures.

test processor UUC l RISC Processor Circuit Pack

PROCR MINOR test processor UUC s RISC Processor Circuit Pack