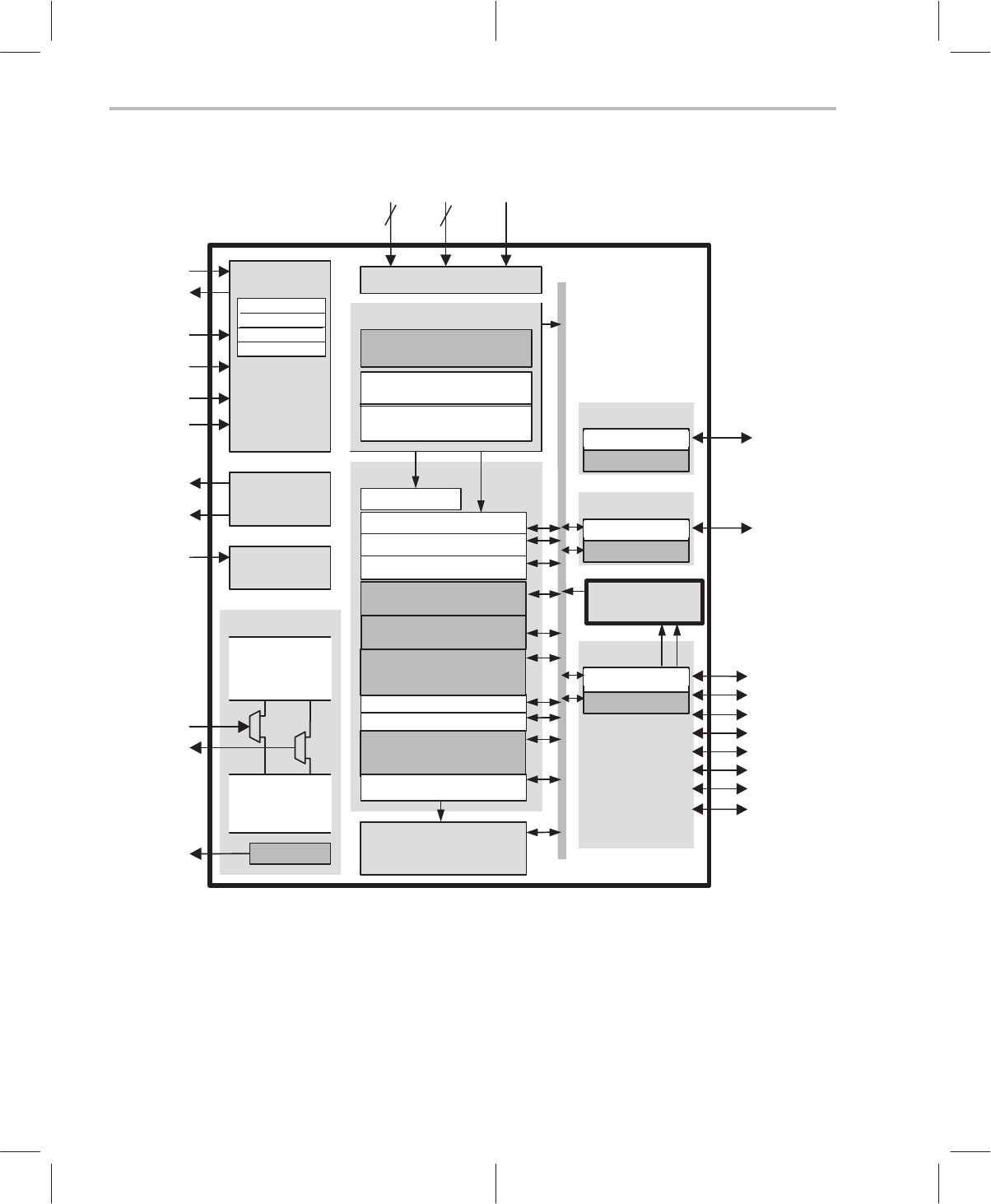

Architecture

B-4

Figure B–1. MSP50C604 Block Diagram

Core

CU Computational Unit

PCU Prog. Counter Unit

Instr. Decoder

TIMER1 PRD1 TIM1

0x3A 0x3B

Clock Control

0x3D

Gen. Control

0x38

RAM 640 x 17 bit

(data)

0x0000 to

0x027F

Power

V

PP

V

DD

V

SS

C port I/0

Control

0x14

DATA

0x10

/

8

PC

0..7

Initialization

Logic

RESET

DAC

0x30

32 Ohm PDM

DAC

M

DAC

P

SYNC

TEST

Scan Interface

SCAN

IN

SCAN

OUT

SCAN

CLK

(EP)

ROM 32k x (16 + 1) bit

User ROM

0x0800 to

0x7FEF

INT vectors

0x7FF0 to

0x7FFF

Test–Area

0x0000 to

(reserved) 0x07FF

D port I/0

Control

0x1C

DATA

0x18

Comparator

1 bit:

PD

5

vs.

PD

4

+–

OSC Reference

PLL Filter

PLL

OSC

OUT

Crystal

Referenced

32.768 kHz

Resistor

Trimmed

32 kHz nominal

OSC

IN

or

or

Break Point

Emulation

OTP Program

Serial Comm.

TIMER2 PRD2 TIM2

0x3E 0x3F

Interrupt Processor

FLAG MASK

0x39 0x38

DMAU

Data Mem. Addr.

55

PGM

PULSE

(C604 only)

(P614 only)

(P614 only)

INRDY/PD

0

OUTRDY/PD

1

STROBE/PD

2

R/WZ/PD

3

PD

4

PD

5

PD

6

PD

7

G port I/0

Control

0x14

DATA

0x10

PG

0

RTOTRIM Register

0x2F

DAC Data/Control

ControlData

0x34 0x30