Instruction Classification

4-41

Assembly Language Instructions

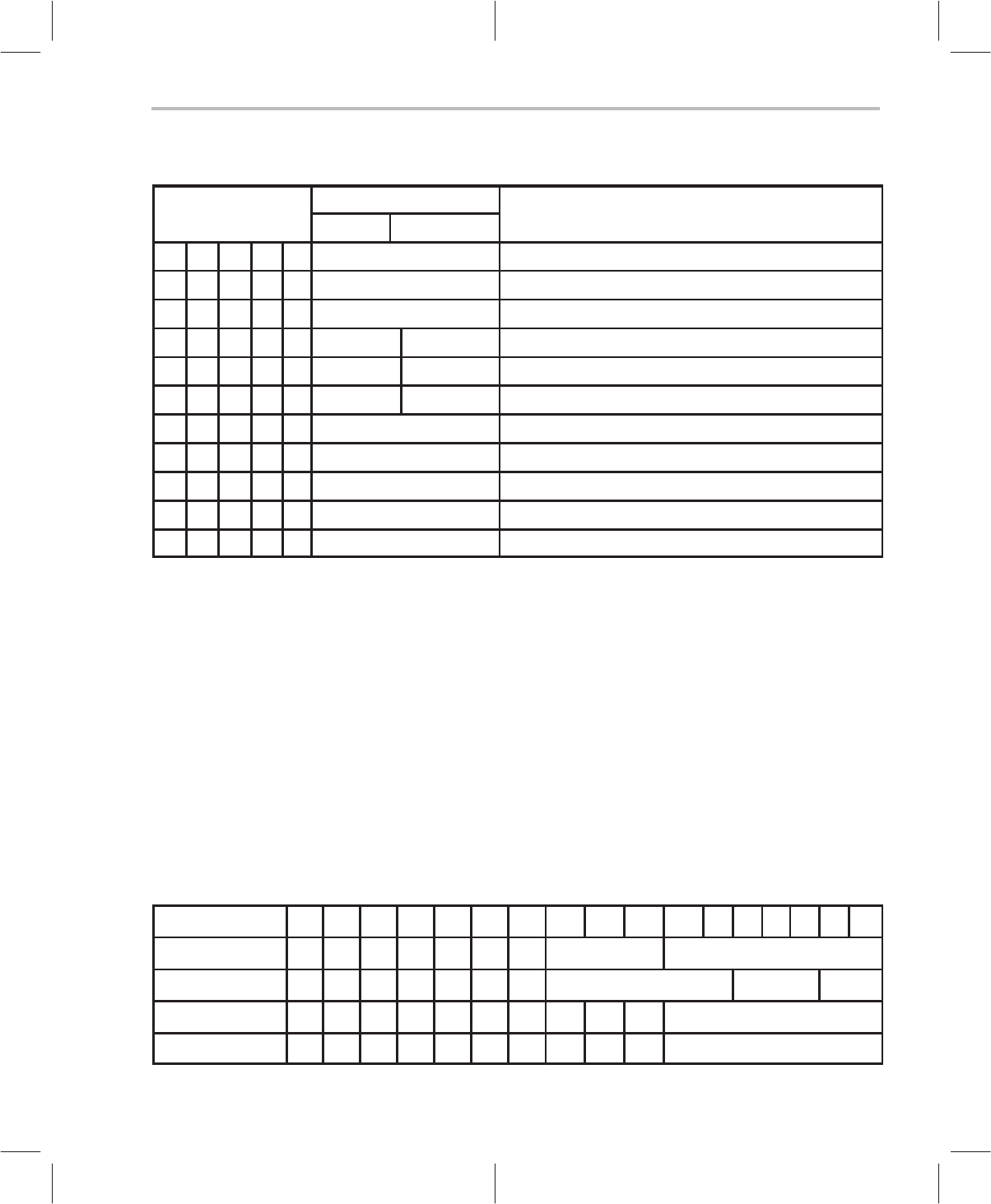

Table 4–31. Class 7 Instruction Encoding and Description (Continued)

cc

cc names

Description

cc

cc name Not cc name

1 0 1 0 1 Unconditional

1 0 1 1 0 Not assigned

1 0 1 1 1 Not assigned

1 1 0 0 0 XZ XNZ Conditional on XSF

1 1 0 0 1 XS XNS Conditional on XZF

1 1 0 1 0 XG XNG Conditional on ! XSF and ! XZF

1 1 0 1 1 Not assigned

1 1 1 0 0 Not assigned

1 1 1 0 1 Not assigned

1 1 1 1 0 Not assigned

1 1 1 1 1 Not assigned

4.4.8 Class 8 Instructions: Logic and Bit

This class of instructions provides a flexible and efficient means to make

complex logical decisions. Instead of making a sequence of single bit

decisions and constructing a logical statement through a branch decision tree,

the program can sequentially combine several status conditions to directly

construct a final logic value (TF1 or TF2) which can be used to control a

subsequent branch or call. This class includes two subclasses. Class 8a

instructions update one of the test flags (TF1 or TF2) with a logical combination

of the old test flag value and an addressed memory flag value. Subclass 8b

provides a flexible means of logically combining the test flag (TF1 or TF2) with

a status condition and storing the results back to the test flag.

Table 4–32. Class 8a Instruction Encoding

Bit 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Class 8a 1 0 0 1 1

flg Not

C8a

flagadrs

Class 8b 1 0 0 1 0

flg Not cc

Rx C8b

RFLAG {

flagadrs

} 1 0 0 1 1 0 0 0 1 1

flagadrs

SFLAG {

flagadrs

} 1 0 0 1 1 1 0 1 0 1

flagadrs