Individual Instruction Descriptions

4-155

Assembly Language Instructions

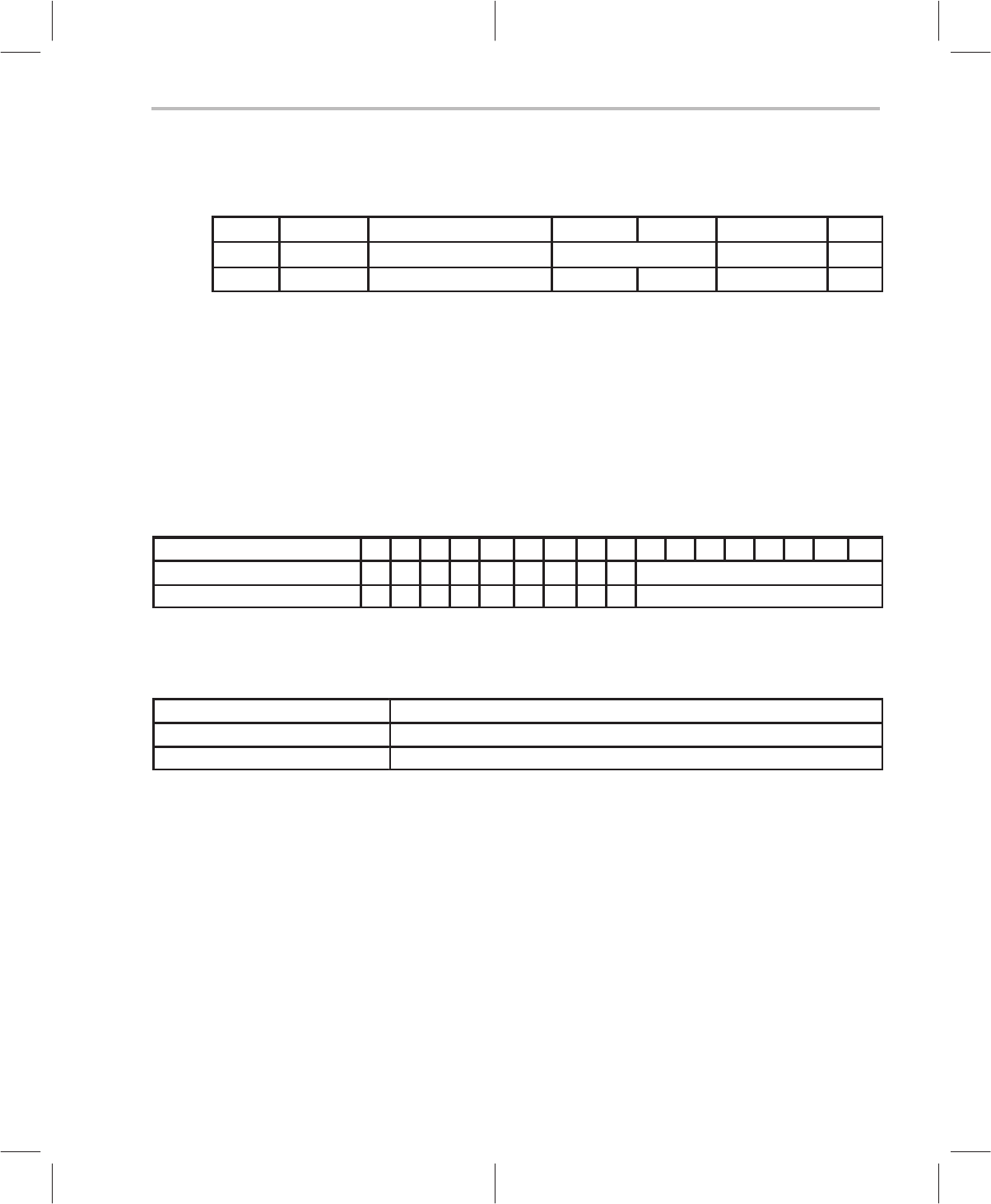

4.14.60 RPT Repeat Next Instruction

Syntax

[label] name src

Clock,

clk

Word,

w

With RPT,

clk

Class

RPT {

adrs

}

8

Table 4–46 N/R 5

RPT

imm8

1 1 N/R 9b

Execution IF RPT {

adrs

}

8

load

src

to repeat counter.

ELSE

load

imm8

to repeat counter.

(

mask interrupt

)

repeat next instruction (repeat counter value + 2) times.

PC ⇐ PC +

w

(next instruction)+1

Flags Affected None

Opcode

Instructions 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RPT {

adrs

}

8

1 1 0 1 1 1 1 1 0

adrs

RPT

imm8

1 1 1 1 1 1 0 0 0

imm8

Description Loads

src

value to repeat counter. Execute next instruction

src

value + 2 times.

Interrupts are queued during RPT instruction. Queued interrupts are serviced

after execution completes.

Syntax Description

RPT {

adrs

}

8

Load data memory byte to repeat counter, repeat next instruction

RPT

imm8

Load immediate byte to repeat counter, repeat next instruction

See Also BEGLOOP, ENDLOOP

Example 4.14.60.1 RPT *0x0100 * 2

MOV *R1++, A0, ++A

Loads the repeat counter with value stored in word data memory location 0x0100. Only 8 bits of data

from this location are used. The next instruction stores content of A0 to data memory address pointed

by R1. Since R1 post increments and A0 preincrements in this instruction, the overall effect of executing

this instruction with RPT is to store accumulator contents to consecutive data memory locations. See

MOV instruction for detail of various syntax of MOV instruction.

Example 4.14.60.2 RPT 200

NOP

Repeat the NOP instruction 202 times (provided the next instruction is repeatable). This causes 203

instruction cycle delay (including 1 cycle for the RPT instruction).