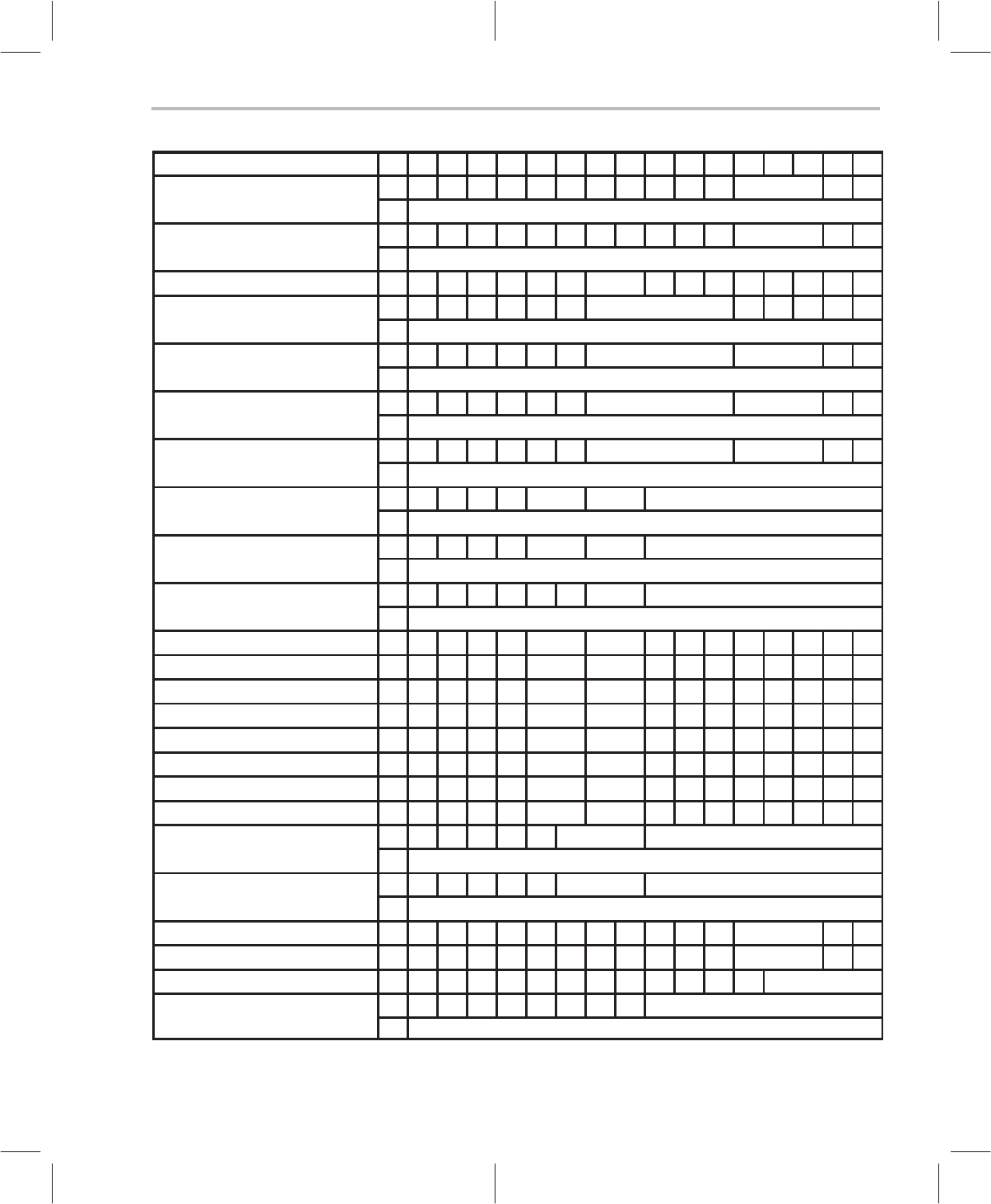

Instruction Set Encoding

4-189

Assembly Language Instructions

Instructions 012345678910111213141516

JMP

pma16

, R

x

––

1 0 0 0 0 0 0 1 0 1 0 1 R

x

1 0

x

pma16

JMP

pma16

, R

x

++R5

1 0 0 0 0 0 0 1 0 1 0 1 R

x

1 1

x

pma16

JMP *A

n

1 0 0 0 1 0 0 A

n

0 0 0 0 0 0 0 0

J

cc

pma16

1 0 0 0 0 0

Not cc

0 0 0 0 0

x

pma16

J

cc

pma16

, R

x

++

1 0 0 0 0 0

Not cc

R

x

0 1

x

pma16

J

cc

pma16

, R

x

––

1 0 0 0 0 0

Not cc

R

x

1 0

x

pma16

J

cc

pma16

, R

x

++R5

1 0 0 0 0 0

Not cc

R

x

1 1

x

pma16

MOV {

adrs

}, A

n

[~] [,

next A

]

0 0 1 1 A~

next A

A

n adrs

x

dma16

(for direct) or

offset16

(long relative) [see section 4.13]

MOV A

n

[~], {

adrs

} [

, next A

]

0 0 1 0 A~

next A

A

n adrs

x

dma16

(for direct) or

offset16

(long relative) [see section 4.13]

MOV {

adrs

}, *A

n

0 1 0 1 1 1 0 A

n adrs

x

dma16

(for direct) or

offset16

(long relative) [see section 4.13]

MOV A

n

[~],

imm16

[

, next A

] 1 1 1 0 0

next A

A

n

0 0 1 0 0 1 0 ~A

MOV MR,

imm16

[,

next A

] 1 1 1 0 0

next A

A

n

1 1 1 0 0 1 0 0

MOV A

n

, A

n

~ [,

next A

] 1 1 1 0 0

next A

A

n

0 0 1 1 1 0 A~ ~A

MOV A

n

[~], PH [,

next A

] 1 1 1 0 0

next A

A

n

0 1 1 1 0 0 A~ ~A

MOV SV, A

n

[~] [,

next A

] 1 1 1 0 0

next A

A

n

1 0 1 0 0 0 A~ 0

MOV PH, A

n

[~] [,

next A

] 1 1 1 0 0

next A

A

n

1 0 1 0 1 0 A~ 0

MOV A

n

[~], *A

n

[~] [

, next A

] 1 1 1 0 0

next A

A

n

0 0 0 1 0 0 A~ ~A

MOV MR, A

n

[~] [,

next A

] 1 1 1 0 0

next A

A

n

1 0 1 1 0 0 A~ 0

MOV {

adrs

}, R

x

1 1 1 1 0 0 R

x

{

adrs

}

x

dma16

(for direct) or

offset16

(long relative) [see section 4.13]

MOV R

x

, {

adrs

}

1 1 1 1 0 1 R

x

{

adrs

}

x

dma16

(for direct) or

offset16

(long relative) [see section 4.13]

MOV R

x

,

imm16

1 1 1 1 1 1 1 0 0 0 1 0 R

x

0 0

MOV R

x

, R5 1 1 1 1 1 1 1 0 0 1 1 0 R

x

0 0

MOV SV,

imm4

1 1 1 1 1 1 0 1 0 0 0 0 0

imm4

MOV SV, {

adrs

}

†

1 1 0 1 1 0 0 0 0

adrs

x

dma16

(for direct) or

offset16

(long relative) [see section 4.13]

†

Signed multiplier mode resets UM (bit 1 in status register ) to 0