S

SPICTL.0

SPI INT FLAG

SPI INT

ENA

SPISTS.6

S

Clock

Polarity

Talk

LSPCLK

456 123 0

0123

SPI Bit Rate

State Control

SPIRXBUF

Buffer Register

Clock

Phase

Receiver

Overrun Flag

SPICTL.4

Overrun

INT ENA

SPICCR.3 − 0

SPIBRR.6 − 0

SPICCR.6 SPICTL.3

SPIDAT.15 − 0

SPICTL.1

M

S

M

Master/Slave

SPISTS.7

SPIDAT

Data Register

M

S

SPICTL.2

SPI Char

SPISIMO

SPISOMI

SPICLK

SW2

S

M

M

S

SW3

To CPU

M

SW1

SPITXBUF

Buffer Register

RX FIFO _0

RX FIFO _1

−−−−−

RX FIFO _15

TX FIFO registers

TX FIFO _0

TX FIFO _1

−−−−−

TX FIFO _15

RX FIFO registers

16

16

16

TX Interrupt

Logic

RX Interrupt

Logic

SPIINT/SPIRXINT

SPITXINT

SPIFFOVF FLAG

SPIFFRX.15

16

TX FIFO Interrupt

RX FIFO Interrupt

SPIRXBUF

SPITXBUF

SPIFFTX.14

SPIFFENA

SPISTE

(A)

TMS320F2809, TMS320F2808, TMS320F2806

TMS320F2802, TMS320F2801, TMS320C2802

TMS320C2801, TMS320F28016, TMS320F28015

www.ti.com

SPRS230L–OCTOBER 2003–REVISED DECEMBER 2009

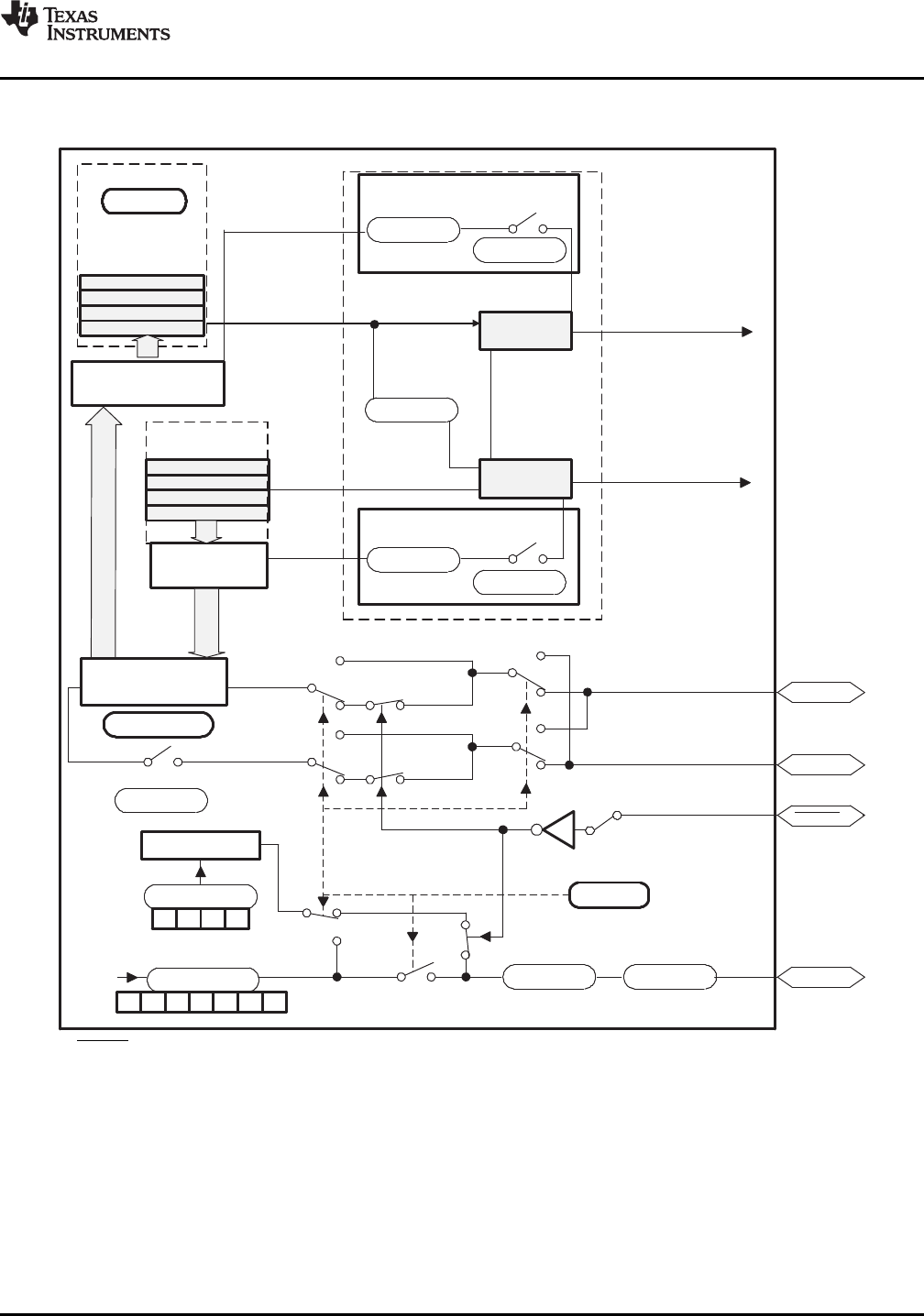

Figure 4-14 is a block diagram of the SPI in slave mode.

A. SPISTE is driven low by the master for a slave device.

Figure 4-14. SPI Module Block Diagram (Slave Mode)

Copyright © 2003–2009, Texas Instruments Incorporated Peripherals 79

Submit Documentation Feedback

Product Folder Link(s): TMS320F2809 TMS320F2808 TMS320F2806 TMS320F2802 TMS320F2801 TMS320C2802

TMS320C2801 TMS320F28016 TMS320F28015