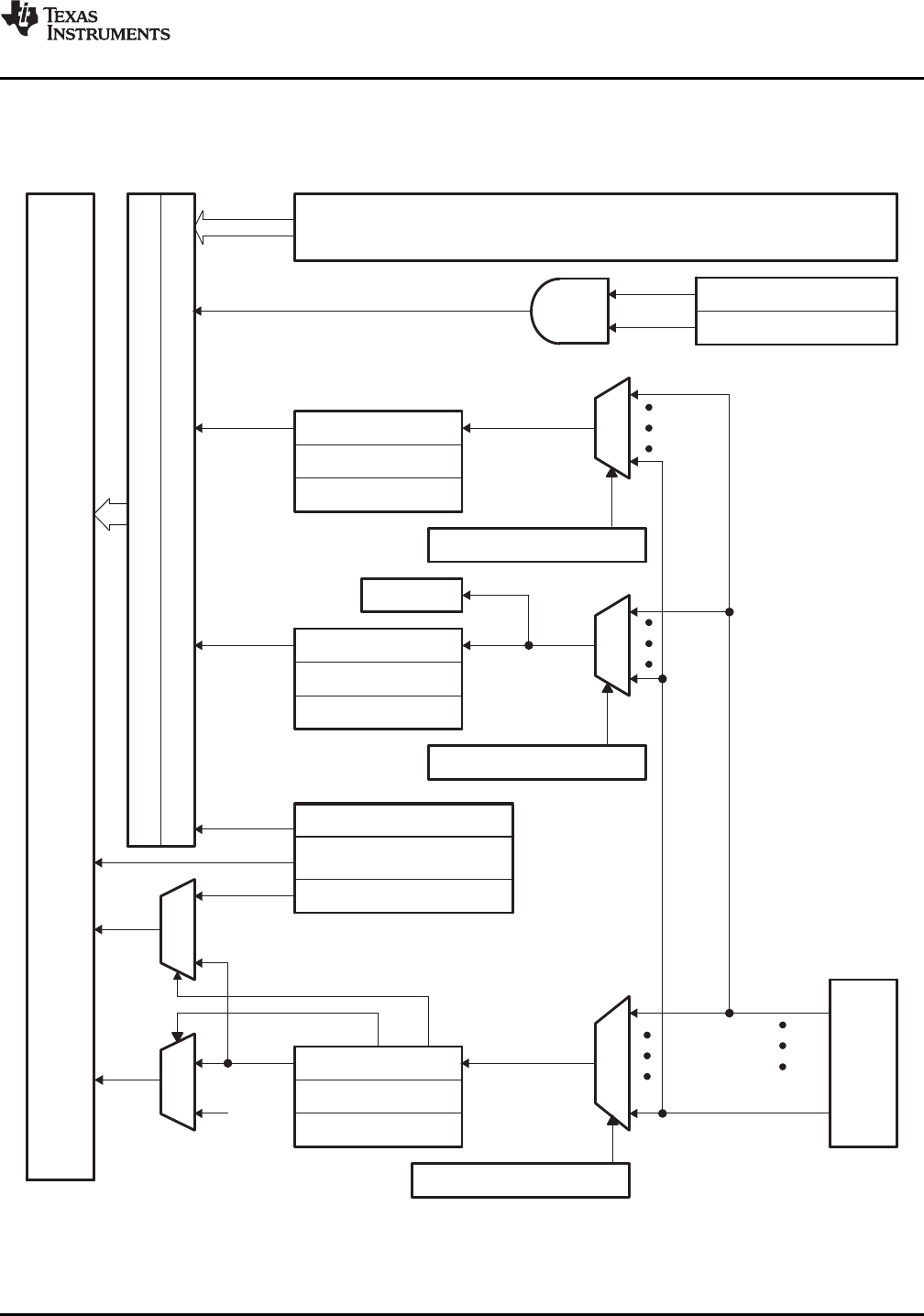

XINT2

C28

CPU

CPUTIMER2

(ReservedforDSP/BIOS)

CPUTIMER0

Watchdog

Peripherals

(SPI,SCI,I2C,eCAN,ePWM,eCAP,eQEP,ADC)

TINT0

InterruptControl

XNMICR(15:0)

XINT1

InterruptControl

XINT1

XINT1CR(15:0)

InterruptControl

XINT2

XINT2CR(15:0)

GPIO

MUX

WDINT

INT1to

INT12

INT13

INT14

NMI

XINT1CTR(15:0)

XINT2CTR(15:0)

XNMICTR(15:0)

CPUTIMER1

TINT2

LowPowerModes

LPMINT

WAKEINT

TINT1

int13_select

XNMI_XINT13

GPIO0.int

GPIO31.int

ADC

XINT2SOC

GPIOXINT1SEL(4:0)

GPIOXINT2SEL(4:0)

GPIOXNMISEL(4:0)

nmi_select

1

MUX

MUX

PIE

96Interrupts

MUX

MUX

MUX

TMS320F2809, TMS320F2808, TMS320F2806

TMS320F2802, TMS320F2801, TMS320C2802

TMS320C2801, TMS320F28016, TMS320F28015

www.ti.com

SPRS230L–OCTOBER 2003–REVISED DECEMBER 2009

When the PIE is enabled, TRAP #1 through TRAP #12 will transfer program control to the interrupt service

routine corresponding to the first vector within the PIE group. For example: TRAP #1 fetches the vector

from INT1.1, TRAP #2 fetches the vector from INT2.1 and so forth.

Figure 3-7. External and PIE Interrupt Sources

Copyright © 2003–2009, Texas Instruments Incorporated Functional Overview 43

Submit Documentation Feedback

Product Folder Link(s): TMS320F2809 TMS320F2808 TMS320F2806 TMS320F2802 TMS320F2801 TMS320C2802

TMS320C2801 TMS320F28016 TMS320F28015