Analog Input on

Channel Ax

Analog Input on

Channel Bx

ADC Clock

Sample and Hold

SH Pulse

t

SH

t

dschA0_n

t

dschB0_n

t

dschB0_n+1

Sample n

Sample n+1

Sample n+2

t

dschA0_n+1

t

d(SH)

ADC Event Trigger from

ePWM or Other Sources

SMODE Bit

TMS320F2809, TMS320F2808, TMS320F2806

TMS320F2802, TMS320F2801, TMS320C2802

TMS320C2801, TMS320F28016, TMS320F28015

www.ti.com

SPRS230L–OCTOBER 2003–REVISED DECEMBER 2009

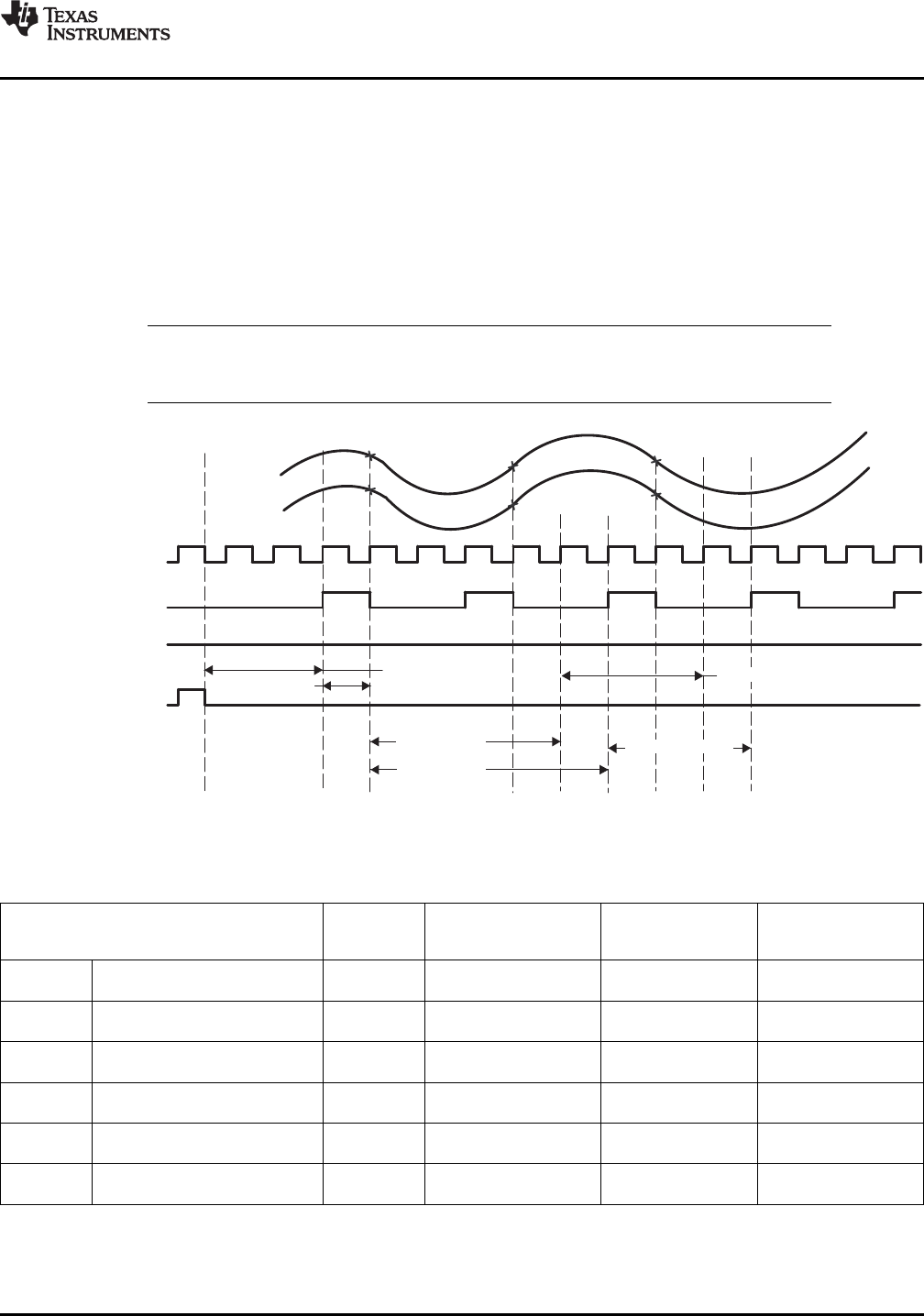

6.10.7.4 Simultaneous Sampling Mode (Dual-Channel) (SMODE = 1)

In simultaneous mode, the ADC can continuously convert input signals on any one pair of channels

(A0/B0 to A7/B7). The ADC can start conversions on event triggers from the ePWM, software trigger, or

from an external ADCSOC signal. If the SMODE bit is 1, the ADC will do conversions on two selected

channels on every Sample/Hold pulse. The conversion time and latency of the result register update are

explained below. The ADC interrupt flags are set a few SYSCLKOUT cycles after the Result register

update. The selected channels will be sampled simultaneously at the falling edge of the Sample/Hold

pulse. The Sample/Hold pulse width can be programmed to be 1 ADC clock wide (minimum) or 16 ADC

clocks wide (maximum).

NOTE

In simultaneous mode, the ADCIN channel pair select has to be A0/B0, A1/B1, ..., A7/B7,

and not in other combinations (such as A1/B3, etc.).

Figure 6-27. Simultaneous Sampling Mode Timing

Table 6-42. Simultaneous Sampling Mode Timing

AT 12.5 MHz

SAMPLE n SAMPLE n + 1 ADC CLOCK, REMARKS

t

c(ADCCLK)

= 80 ns

t

d(SH)

Delay time from event trigger to 2.5t

c(ADCCLK)

sampling

t

SH

Sample/Hold width/Acquisition (1 + Acqps) * 80 ns with Acqps = 0 Acqps value = 0–15

Width t

c(ADCCLK)

ADCTRL1[8:11]

t

d(schA0_n)

Delay time for first result to 4t

c(ADCCLK)

320 ns

appear in Result register

t

d(schB0_n )

Delay time for first result to 5t

c(ADCCLK)

400 ns

appear in Result register

t

d(schA0_n+1)

Delay time for successive results (3 + Acqps) * t

c(ADCCLK)

240 ns

to appear in Result register

t

d(schB0_n+1 )

Delay time for successive results (3 + Acqps) * t

c(ADCCLK)

240 ns

to appear in Result register

Copyright © 2003–2009, Texas Instruments Incorporated Electrical Specifications 129

Submit Documentation Feedback

Product Folder Link(s): TMS320F2809 TMS320F2808 TMS320F2806 TMS320F2802 TMS320F2801 TMS320C2802

TMS320C2801 TMS320F28016 TMS320F28015