TMS320F2809, TMS320F2808, TMS320F2806

TMS320F2802, TMS320F2801, TMS320C2802

TMS320C2801, TMS320F28016, TMS320F28015

www.ti.com

SPRS230L–OCTOBER 2003–REVISED DECEMBER 2009

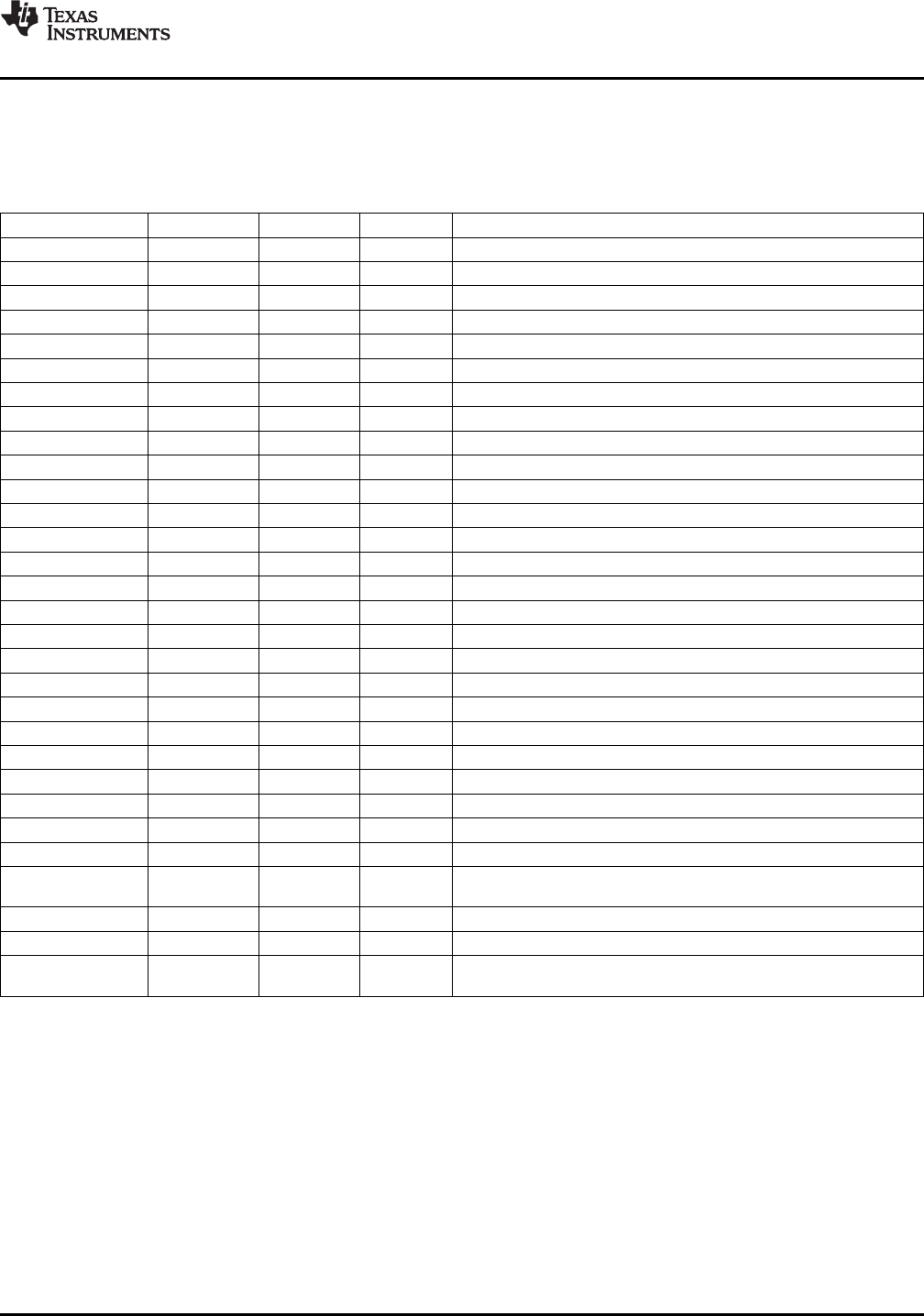

4.6.2 ADC Registers

The ADC operation is configured, controlled, and monitored by the registers listed in Table 4-5.

Table 4-5. ADC Registers

(1)

NAME ADDRESS

(1)

ADDRESS

(2)

SIZE (x16) DESCRIPTION

ADCTRL1 0x7100 1 ADC Control Register 1

ADCTRL2 0x7101 1 ADC Control Register 2

ADCMAXCONV 0x7102 1 ADC Maximum Conversion Channels Register

ADCCHSELSEQ1 0x7103 1 ADC Channel Select Sequencing Control Register 1

ADCCHSELSEQ2 0x7104 1 ADC Channel Select Sequencing Control Register 2

ADCCHSELSEQ3 0x7105 1 ADC Channel Select Sequencing Control Register 3

ADCCHSELSEQ4 0x7106 1 ADC Channel Select Sequencing Control Register 4

ADCASEQSR 0x7107 1 ADC Auto-Sequence Status Register

ADCRESULT0 0x7108 0x0B00 1 ADC Conversion Result Buffer Register 0

ADCRESULT1 0x7109 0x0B01 1 ADC Conversion Result Buffer Register 1

ADCRESULT2 0x710A 0x0B02 1 ADC Conversion Result Buffer Register 2

ADCRESULT3 0x710B 0x0B03 1 ADC Conversion Result Buffer Register 3

ADCRESULT4 0x710C 0x0B04 1 ADC Conversion Result Buffer Register 4

ADCRESULT5 0x710D 0x0B05 1 ADC Conversion Result Buffer Register 5

ADCRESULT6 0x710E 0x0B06 1 ADC Conversion Result Buffer Register 6

ADCRESULT7 0x710F 0x0B07 1 ADC Conversion Result Buffer Register 7

ADCRESULT8 0x7110 0x0B08 1 ADC Conversion Result Buffer Register 8

ADCRESULT9 0x7111 0x0B09 1 ADC Conversion Result Buffer Register 9

ADCRESULT10 0x7112 0x0B0A 1 ADC Conversion Result Buffer Register 10

ADCRESULT11 0x7113 0x0B0B 1 ADC Conversion Result Buffer Register 11

ADCRESULT12 0x7114 0x0B0C 1 ADC Conversion Result Buffer Register 12

ADCRESULT13 0x7115 0x0B0D 1 ADC Conversion Result Buffer Register 13

ADCRESULT14 0x7116 0x0B0E 1 ADC Conversion Result Buffer Register 14

ADCRESULT15 0x7117 0x0B0F 1 ADC Conversion Result Buffer Register 15

ADCTRL3 0x7118 1 ADC Control Register 3

ADCST 0x7119 1 ADC Status Register

0x711A –

Reserved 2 Reserved

0x711B

ADCREFSEL 0x711C 1 ADC Reference Select Register

ADCOFFTRIM 0x711D 1 ADC Offset Trim Register

0x711E –

Reserved 2 Reserved

0x711F

(1) The registers in this column are Peripheral Frame 2 Registers.

(2) The ADC result registers are dual mapped in the 280x DSP. Locations in Peripheral Frame 2 (0x7108-0x7117) are 2 wait-states and left

justified. Locations in Peripheral frame 0 space (0x0B00-0x0B0F) are 0 wait sates and right justified. During high-speed/continuous

conversion use of the ADC, use the 0 wait-state locations for fast transfer of ADC results to user memory.

Copyright © 2003–2009, Texas Instruments Incorporated Peripherals 67

Submit Documentation Feedback

Product Folder Link(s): TMS320F2809 TMS320F2808 TMS320F2806 TMS320F2802 TMS320F2801 TMS320C2802

TMS320C2801 TMS320F28016 TMS320F28015