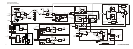

sk789b

MEMORY

SERIAL INTERFACE

(INTERNAL)

INTERNAL

DATA BUS

SWITCH & LEDS

INTERNAL

DATA BUS

SELF TEST

LEDS

CONFIG

SWITCH

INT ADDR

BUS

SERIAL I/O

BUS

SERIAL I/O

INTERFACE

L SERIAL

I/O INT

A14 CPU/MOTHERBOARD BLOCK DIAGRAM (1 OF 2)

CPU CLOCK

CPU INTERFACE

CPU

SERIAL INTERFACE

(EXTERNAL)

32.77 kHz

CLOCK

RS-232

SERIAL

INTERFACE

+5V

J8-2

J8-8

J8-3

J8-7

J8-4

J8-5

RECV

CTS

XMIT

RTS

+5V

RXD

TXD

L PRESET

L HALT

FROM: AUXILIARY

INTERFACE

ADDRESS

BUFFERS

DATA

BUFFERS

BUS

CONTROL

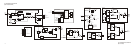

BOOT

ROM

ADDRESS BUS

CPU DATA BUS

SERIAL I/O BUS

CPU DATA BUS

INT CONT

BUS

MEM ADDR

BUS

MEM DATA

BUS

INT ADDR

BUS

INTERNAL DATA

BUS

FLASH

MEMORY

1M X 32

EEROM

64K X 8

NONVOLATILE

RAM

128K X 16

RAM

512 X 16

MEM ADDR

BUS

MEM ADDR

BUS

MEM ADDR

BUS

MEM ADDR

BUS

MEM DATA

BUS

MEM DATA

BUS

MEM DATA

BUS

MEM DATA

BUS

ATTEN ENABLE

ATTEN CLK

ATTEN DATA

ATTENUATOR & RPP

INTERFACE

TO: DAUGHTER

BOARD

L DCC ALT

PWR SEL

TRIG INT

INTERNAL DATA BUS

HF

ATTEN

CONTROL

ATTEN

SENSE

L RPP INT

L RPP RESET

HP- IB INTERFACE

INTERNAL

DATA BUS

INT ADDR

BUS

HP-IB

INTERFACE

TO:

HP-IB

L HP-IB INT

A14 CPU/MOTHERBOARD BLOCK DIAGRAM (1 0F 2)

DIGITAL SIGNAL PROCESSOR (DSP)

ABUS

INT MOD

INTERNAL MODULATION DAC

DSP TRIG

OUT

L DSP INT

CLK OUT

RESET

TRIG INT

INT ADDR BUS

DSP ADDR BUS

DSP DATA BUS

INTERNAL DATA BUS

16 MHz

CLOCK

DSP/CPU

INTERFACE

DIGITAL

SIGNAL

PROCESSOR

SERIAL INTERFACE

DSP ADDR BUS

DSP RAM

DSP DATA BUS

DSP

RAM

32K X 8

+

TP705

TP706

TO: DAUGHTER

BOARD

ANALOG TO DIGITAL CONVERTER (ADC)

SWEEP RAMP

SERIAL INTERFACE

+

SWEEP

OUT

J9

+10V REF

SWEEP RAMP

A BUS

BUF ABUS

BUF ABUS

ABUS

ABUS RTN

TP703

TP702

ADC IN

TP704

+5V

ADC

INT_I_MOD

INT_I_MOD

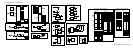

P102

P103

EXT. DATA & CLOCK IN

P5

P6

P7

JI-49

J2-49

J3-49

J4-49

JI-50

J2-50

J3-50

J4-50

JI-100

J2-100

J3-100

J4-100

DATA

CLOCK

SYMB_SYNC

MECH.

ELEC.

REF ENABLE

REF CLK

REF DATA

SYNTH ENABLE

SNTH CLK

SYNTH DATA

OUTPUT ENABLE

OUTPUT CLK

OUTPUT DATA

INT_I_MOD1

INT_Q_MOD1

SPARE_I_DATA

SPARE_I_EN

J18

2

3

4

7

8

TO PULSE

MODULATOR

OPTION 1E6

FLASH PROGRAM

VOLTAGE

INTERNAL

DATA BUS

ENABLE

FLASH

PROGRAM

VOLTAGE

REG

+15V

FLASH

VPP

TP303

PROGRAM = +12V

IRQ1

IRQ2

IRQ3

IRQ4

IRQ7

IRQ6

IRQ5

TP CLK

TPU0

TPU1

TPU2

TPU3

TPU4

TPU5

TPU6

TPU7

TPU8

TPU10

L SERIAL I/O INT

NOT USED

L HP-IB INT

L RPG INT

NOT USED

L KEY INT

NOT USED

10 MHz DIG

COUNTER

CPU TRIG INT

L DSP INT

DIG BUS INT 1

DIG BUS INT 2

DIG BUS INT 3

DIG BUS INT 4

PULSE INT

L RPP INT

CTS

LATN

LEOI

LSRQ

LREN

LIFC

LDAV

NDAC

NRFD

DIO1

DIO2

DIO3

DIO4

DIO5

DIO6

DIO7

DIO8

J7-11

J7-5

J7-10

J7-17

J7-9

J7-6

J7-8

J7-7

J7-1

J7-2

J7-3

J7-4

J7-13

J7-14

J7-15

J7-16

+15V

+12.5V

+5.2V

-12.5V

ACOM

L = LF ATTEN

L=HF ATTEN

ATTEN_405_5

ATTEN_5A_10

ATTEN_10A_40

ATEN XX

ATTEN_20_XX

ATTEN_10B_20

ATTEN_40A_60

ATTEN_5B_XX

J14-17

J14-11

J14-10

J14-9

J14-7

J14-6

J14-5

J14-4

J14-3

J14-2

ATTEN ENABLE

ATTEN CLK

ATTEN DATA

L RPP INT

L RPP RESET

J14-20

J14-19

J14-18

J14-16

J15-2

J14-12

J15-1

J14-1

J14-14

J15-3

J14-15

J15-5

J14-13

J15-4

J14-8

-15V

+5.2VD

J5-24

J5-45

J5-44

J5-70

J5-73

J5-76

J5-20

J5-23

J5-26

J5-18

J5-21

TRIGGER I/O

DSP TRIG OUT

CPU TRIG INT

DCC TRIG INT

TRIG INT

TRIG

ENABLE

TRIG

ENABLE

TRIGGER

IN

J11

TRIGGER

OUT

J10

10 MHz IN/OUT

10 MHz

OUT

10 MHz

IN

J12

J13

FROM:

DAUGHTER

BOARD

TO:

DAUGHTER

BOARD

CPU TRIG OUT

DCC TRIG OUT

TP701

DAC

DAC