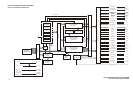

A7 BASEBAND GENERATOR BLOCK DIAGRAM (OPTIONS UN3 & UN4)

A7 BASEBAND GENERATOR BLOCK DIAGRAM (OPTIONS UN3 & UN4)

sk7120a

DAC

I DATA GENERATION

ANALOG FILTERS

(NADC/TETRA/

PDC,PHS,GSM)

p

WRITE DATA

LATCH I CAL

12

12

FORMAT SELECT

p

/4 CONTROL LOGIC

/4 CLK

FORMAT SELECT

CA ADDRESS & CONTROL

I

CAL LATCHES

I

/4 DQPSK

(NADC,TETRA,

PDC,PHS)

p

I

CONSTANT

AMPLITUDE

(GMSK, GFSK

DECT)

ABUS

I OUT

P405

I OUT

PATH CONTROL

LOGIC

I DAC

DATA

MODULATION

ENABLE/SELECT

TO I-OUT

INT I MOD OUT

P301-2

Q DATA GENERATION

WRITE DATA

LATCH Q CAL

12

Q

CAL LATCHES

Q OUT

p

p

12

FORMAT SELECT

/4 CONTROL LOGIC

/4 CLK

FORMAT SELECT

CA ADDRESS & CONTROL

Q

/4 DQPSK

(NADC,TETRA,

PDC,PHS)

p

Q

CONSTANT

AMPLITUDE

(GMSK,GFSK,

DECT)

Q DAC

DATA

MODULATION

ENABLE/SELECT

MOD

INVERT

DAC

ANALOG FILTERS

(NADC/TETRA/

PDC,PHS GSM)

ABUS

PATH CONTROL

LOGIC

MOD INVERT

P404

Q OUT

TO Q-OUT

INT Q MOD OUT

P301-53

BURST MOD

EEPROM

DATA

LATCHED

ADDRESS

LATCHED

DATA

CONTROL

LOGIC

DIGITAL INTERFACE

IAB3

P301-26

P301-33

EXT SELECT

L EXT STROBE

P301-82

P301-83

EXT RD L WR

EXT RESET

P301-32

P301-24

IAB0

IAB1

P301-74

P301-25

IAB2

P301-76

IAB4

IAB5

P301-27

P301-77

IAB6

IAB7

P301-78

P301-29

IAB8

IAB9

P301-79

P301-36

IAB10

READ/LWRITE

STROBE

SELECT

RESET

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

P301-19

EXT_DO

EXT_D1

P301-20

P301-70

EXT_D2

EXT_D3

P301-21

P301-71

EXT_D4

EXT_D5

P301-72

P301-23

EXT_D6

P301-73

EXT_D7

D0

DIG BUS INT

(PLL UNLOCKED)

D1

D2

D3

D4

D5

D6

D7

SELECT

CLK

PLL CLK

PLL LOCK SIG

PLL REF

GENERATOR INTERFACE

p

DATA GENERATION CONTROL

CONTROL

LOGIC

BURST

CONTROL LOGIC

BURST PLS

MOD INVERT

CAL ENABLE

LATCH I CAL

LATCH Q CAL

PLL GAIN

EXT REF ENABLE

/4 PMF ENABLE

CA PMF ENABLE

VCO ENABLE

EVENT SELECT

PATH

CONTROL LOGIC

PMF CONTROL

FORMAT SELECT

LBIT_CLK

LATCH ADDRESS

L_BURST

LATCH DATA

PMF

CONTROL

LOGIC

LBIT_CLK

BBG_BIT_CLK

LDATA_CLK

REF

MASTER CLOCK PLL

160 T O 320 MHz

MASTER CLOCK

20 T O

40 MHz

VCO

ENABLE

REFERENCE

REF SELECT

&

DIVIDE

10 MHz DIG

P301-84

FROM MOTHERBOARD

/CPU

13 MHz

FROM 13 MHz IN

P403

F

PLL

DIVIDERS

VCO

ABUS

PLL T UNE

PLL_T UNE

P301-35

DIG BUS INT

(PLL UNLOCKED)

LOOP FILTER

&

LEAD/LAG

P300-6

BURST_GATE

ADJ_TS_PWR_IN

P300-8

P300-10

BB_DATA

SYMBOL_SYNC

P300-12

P300-14

EXT_CLK

14

12

10

8

6

BBG_INT_CLK

P300-18

P300-20

BBG_EN

20

18

P300-22

22

16

BBG_BIT_CLK

P300-16

LOOP

COUNT

&

DIFF

ENCODE

INTERNAL

CLK

MASTER CLOCK

LBIT_CLK

BUFFERED DATA

SYMBOL SYNC INV

PMF CONTROL

p

/4 CLK

SUB_ I_COUNT (3)

PLL LOCK SIG

SUB_I _COUNT (1)

p

CA ADDRESS & CONTROL

/4 CONTROL LOGIC

P300-22

P300-16

SUB_I_COUNT (1)

PLL_CLOCK

L_BURST

BUFFERED_DATA_IN

SYMBOL_SYNC_INV

ABUS

DATA

RC TIME

CONSTANT

LDATA_CLK

ABUS

LCLK

ABUS

BURST

RC TIME

CONSTANT

POWER SUPPLY INPUTS

+15V

+10 VREF

ABUS

-1V_REF

-1 V_REF

+32V

P301-9

P301-14,64

P301-16,66

P301-17,67

P301-12

P301-62

P301-13,63

P301-1,7,54,56

P301-22,28,34,

40,46,69,75,81,

87,93 ,99

+5VA

+5.2V

-5.2V

-5V

-15V

ANALOG

COMMON

DIGITAL

COMMON

+10V

REF

BURST MOD

SWITCH

AND

FILTERS

P301-80

L_DCC_ALT_PWR_SEL

INTL_ALC_HOLD

BURST_PULSE

BURST_ENVELOPE

P301-31

P301-30

P301-57

BURST

ENVELOPE

CONTROL

&

RAM

ENVL_LATCH

LATCH_DATA

BURST_TC

MASTER_CLK

BURST_PLS

CONTROL

LOGIC

DAC_EN

-IV_REF

ENVELOPE

DATA

15

15