TMS320C6202

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS072B – AUGUST 1998 – REVISED AUGUST 1999

62

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

MULTICHANNEL BUFFERED SERIAL PORT TIMING (CONTINUED)

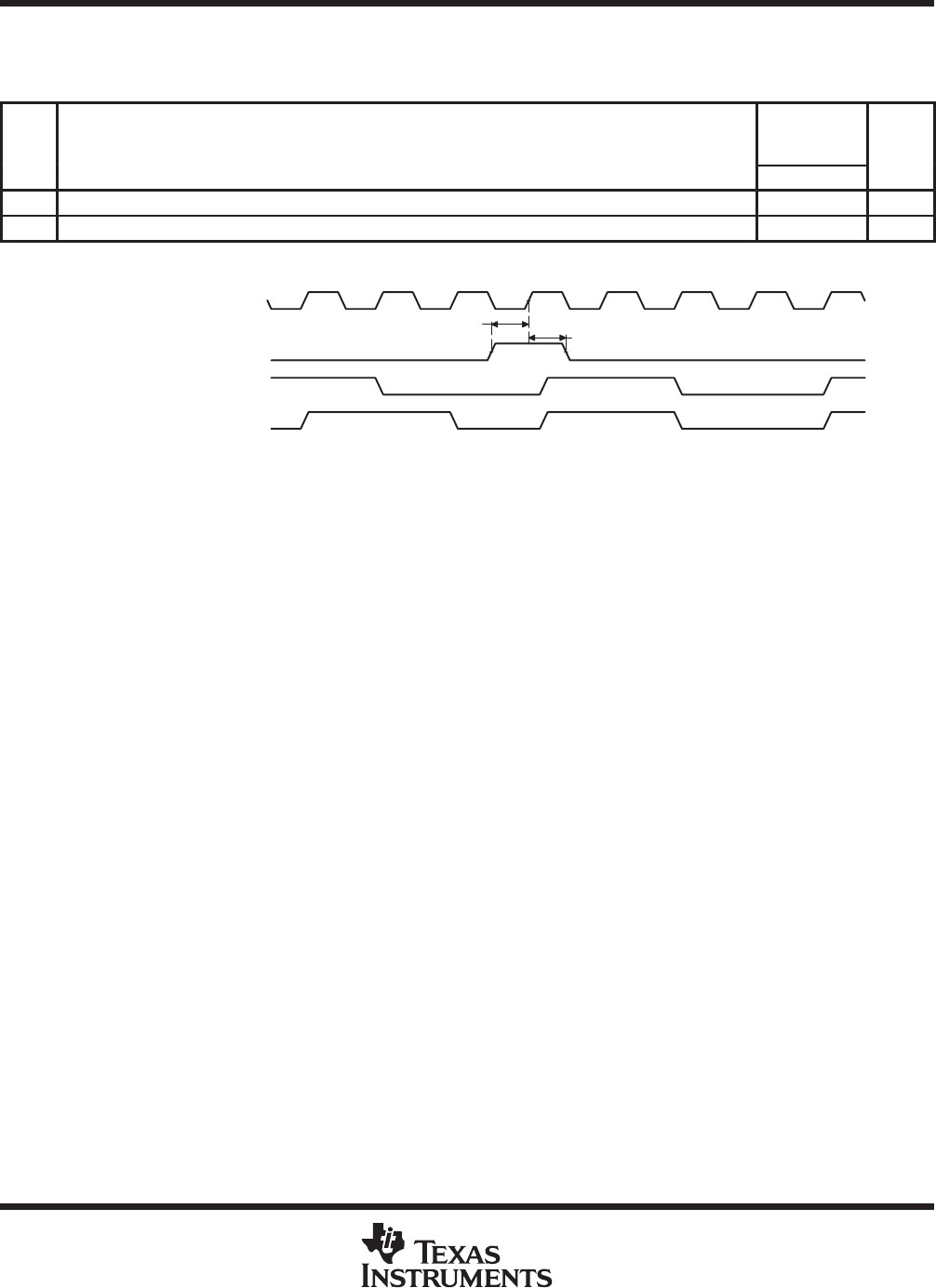

timing requirements for FSR when GSYNC = 1 (see Figure 41)

NO.

’C6202-200

’C6202-233

’C6202-250

UNIT

MIN MAX

1 t

su(FRH-CKSH)

Setup time, FSR high before CLKS high 4 ns

2 t

h(CKSH-FRH)

Hold time, FSR high after CLKS high 4 ns

2

1

CLKS

FSR external

CLKR/X (no need to resync)

CLKR/X(needs resync)

Figure 41. FSR Timing When GSYNC = 1

ADVANCE INFORMATION