TMS320C6202

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS072B – AUGUST 1998 – REVISED AUGUST 1999

12

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

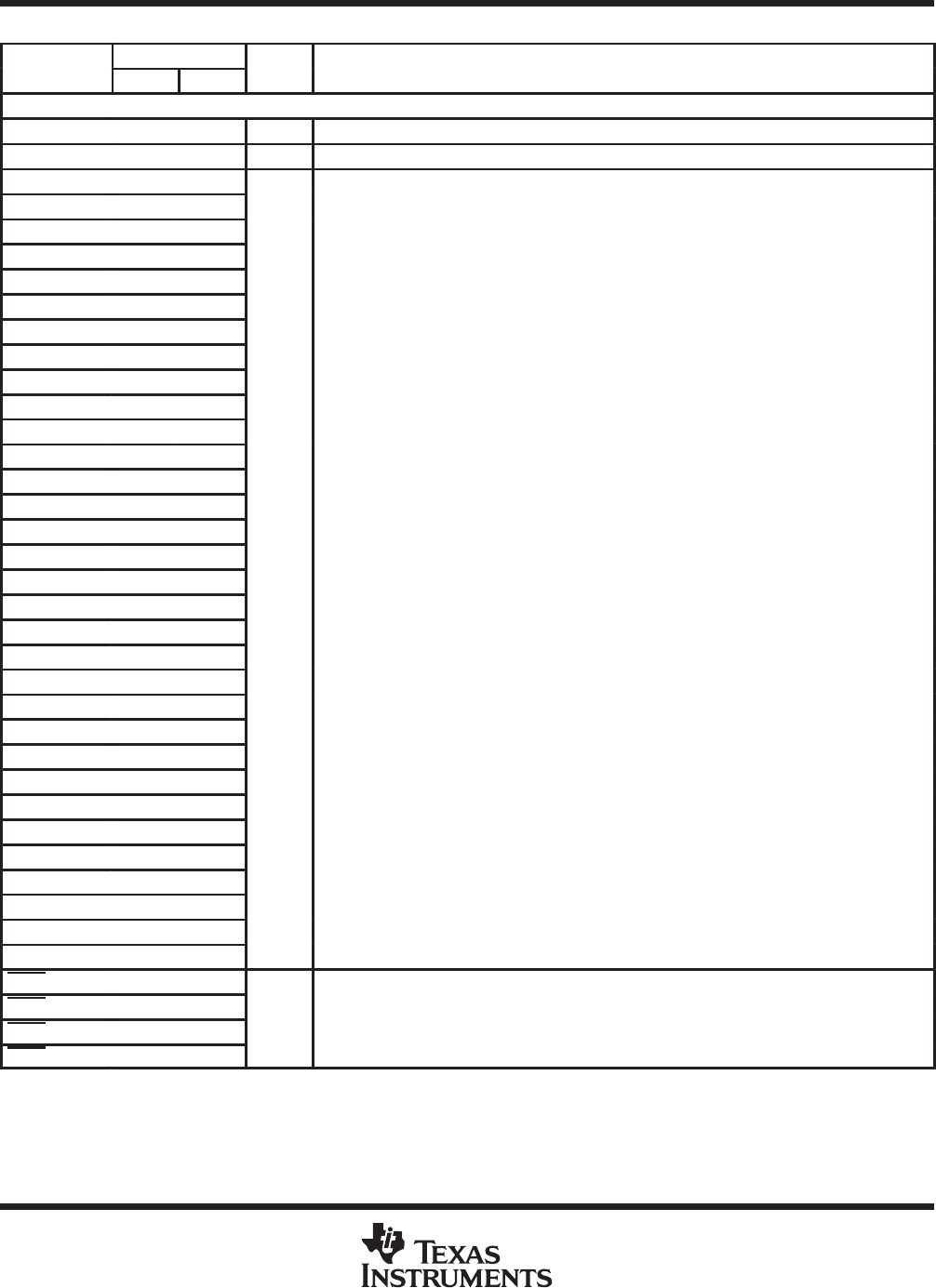

Signal Descriptions (Continued)

SIGNAL

PIN NO.

TYPE

†

DESCRIPTION

NAME

GJL GLS

TYPE

†

DESCRIPTION

EXPANSION BUS

XCLKIN A9 C8 I Expansion bus synchronous host interface clock input

XFCLK B9 A8 O Expansion bus FIFO interface clock output

XD31 D15 C13

XD30 B16 A13

XD29 A17 C14

XD28 B17 B14

XD27 D16 B15

XD26 A18 C15

XD25 B18 A15

XD24 D17 B16

XD23 C18 C16

XD22 A20 A17

XD21 D18 B17

XD20 C19 C17

Ex

p

ansion bus data

XD19 A21 B18

Ex ansion

bus

data

• Used for transfer of data, address, and control

XD18 D19 A19

,,

• Also controls initialization of DSP modes and expansion bus at reset via pullup/pulldown

it

XD17 C20 C18

resistors

–

XCE[3:0] memory ty

p

e

XD16 B21 B19

I/O/Z

–

XCE[3:0]

memory

ty e

– XBLAST polarity

XD15 A22 C19

I/O/Z

y

– XW/R polarity

Ah h ht ti

XD14 D20 B20

– Asynchronous or synchronous host operation

–

Arbitration mode (internal or external)

XD13 B22 A21

– Arbitration

mode

(internal

or

external)

– FIFO mode

XD12 E25 C21

– Little endian/big endian

Boot mode

XD11 F24 D20

–

B

oo

t

mo

d

e

XD10 E26 B22

XD9 F25 D21

XD8 G24 E20

XD7 H23 E21

XD6 F26 D22

XD5 G25 F20

XD4 J23 F21

XD3 G26 E22

XD2 H25 G20

XD1 J24 G21

XD0 K23 G22

XCE3 F2 D2

XCE2 E1 B1

O/Z

Expansion bus I/O port memory space enables

• Enabled by bits 28 29 and 30 of the word address

XCE1 F3 D3

O/Z

•

E

na

bl

e

d

b

y

bit

s

28

,

29

, an

d

30

o

f

th

e wor

d

a

dd

ress

•

O

nl

y

on

e

asse

rt

ed

du

rin

g

a

n

y

I

/O

port

da

t

a

access

XCE0 E2 C2

• Only

one

asserted

during

any

I/O

ort

data

access

†

I = Input, O = Output, Z = High Impedance, S = Supply Voltage, GND = Ground

ADVANCE INFORMATION