TMS320C6202

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS072B – AUGUST 1998 – REVISED AUGUST 1999

37

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

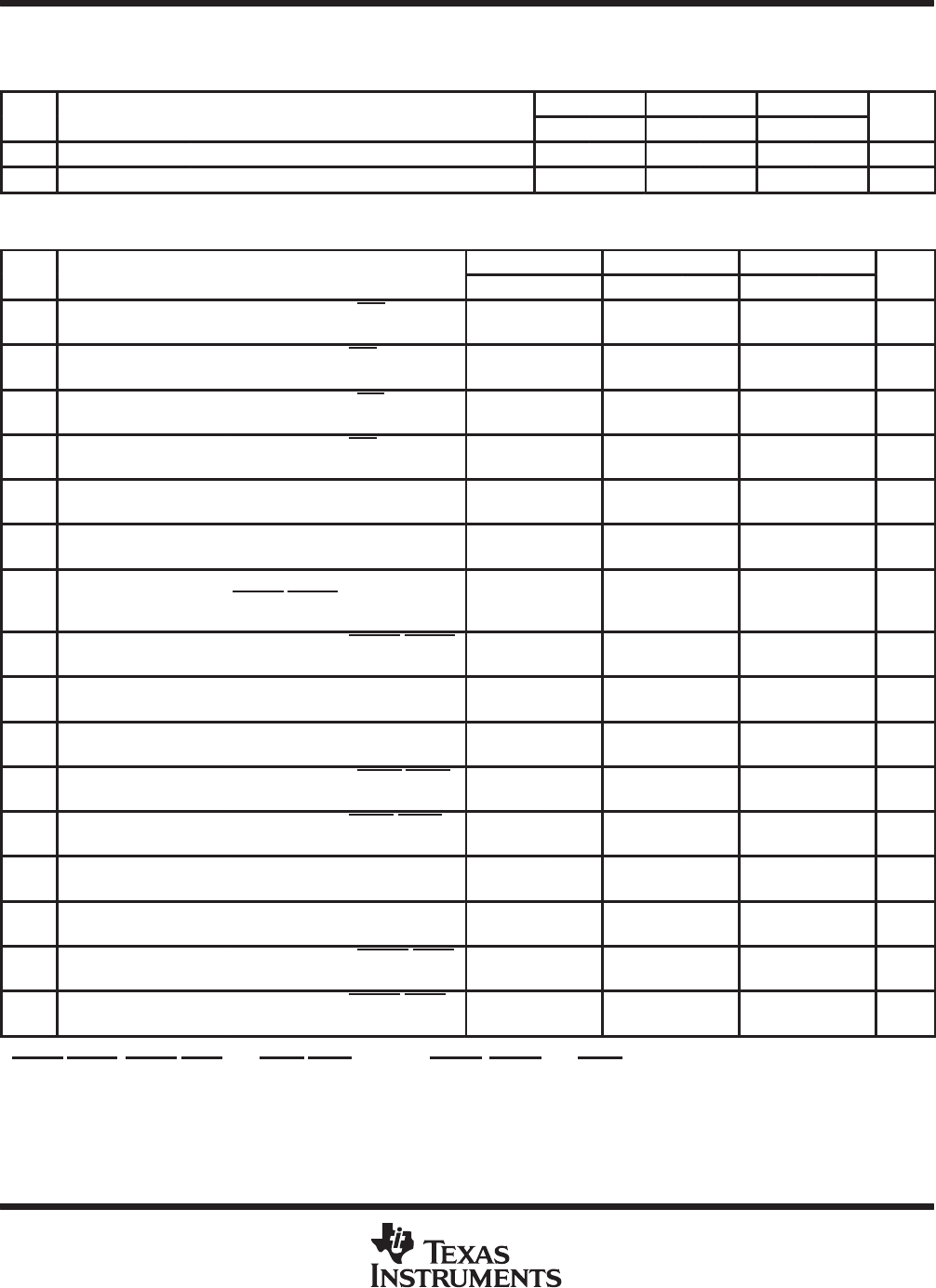

SYNCHRONOUS DRAM TIMING

timing requirements for synchronous DRAM cycles (see Figure 17)

NO

’C6202-200 ’C6202-233 ’C6202-250

UNIT

NO

.

MIN MAX MIN MAX MIN MAX

UNIT

7 t

su(EDV-CKO2H)

Setup time, read EDx valid before CLKOUT2 high 1 1 0.5 ns

8 t

h(CKO2H-EDV)

Hold time, read EDx valid after CLKOUT2 high 3 3 3 ns

switching characteristics for synchronous DRAM cycles

†‡

(see Figure 17–Figure 22)

NO

PARAMETER

’C6202-200 ’C6202-233 ’C6202-250

UNIT

NO

.

PARAMETER

MIN MAX MIN MAX MIN MAX

UNIT

1 t

osu(CEV-CKO2H)

Output setup time, CEx valid

before CLKOUT2 high

2P – 6 2P – 4.6 2P – 4 ns

2 t

oh(CKO2H-CEV)

Output hold time, CEx valid after

CLKOUT2 high

1.5 1.5 1.5 ns

3 t

osu(BEV-CKO2H)

Output setup time, BEx valid

before CLKOUT2 high

2P – 6 2P – 4.6 2P – 4 ns

4 t

oh(CKO2H-BEIV)

Output hold time, BEx invalid after

CLKOUT2 high

1.5 1.5 1.5 ns

5 t

osu(EAV-CKO2H)

Output setup time, EAx valid

before CLKOUT2 high

2P – 6 2P – 4.6 2P – 4 ns

6 t

oh(CKO2H-EAIV)

Output hold time, EAx invalid after

CLKOUT2 high

1.5 1.5 1.5 ns

9 t

osu(CASV-CKO2H)

Output setup time,

SDCAS

/SSADS valid before

CLKOUT2 high

2P – 6 2P – 4.6 2P – 4 ns

10 t

oh(CKO2H-CASV)

Output hold time, SDCAS/SSADS

valid after CLKOUT2 high

1.5 1.5 1.5 ns

11 t

osu(EDV-CKO2H)

Output setup time, EDx valid

before CLKOUT2 high

§

2P – 6 2P – 4.6 2P – 4 ns

12 t

oh(CKO2H-EDIV)

Output hold time, EDx invalid after

CLKOUT2 high

1.5 1.5 1.5 ns

13 t

osu(WEV-CKO2H)

Output setup time, SDWE/SSWE

valid before CLKOUT2 high

2P – 6 2P – 4.6 2P – 4 ns

14 t

oh(CKO2H-WEV)

Output hold time, SDWE/SSWE

valid after CLKOUT2 high

1.5 1.5 1.5 ns

15 t

osu(SDA10V-CKO2H)

Output setup time, SDA10 valid

before CLKOUT2 high

2P – 6 2P – 4.6 2P – 4 ns

16 t

oh(CKO2H-SDA10IV)

Output hold time, SDA10 invalid

after CLKOUT2 high

1.5 1.5 1.5 ns

17 t

osu(RASV-CKO2H)

Output setup time, SDRAS/SSOE

valid before CLKOUT2 high

2P – 6 2P – 4.6 2P – 4 ns

18 t

oh(CKO2H-RASV)

Output hold time, SDRAS/SSOE

valid after CLKOUT2 high

1.5 1.5 1.5 ns

†

P = 1/CPU clock frequency in ns. For example, when running parts at 250 MHz, use P = 4 ns.

‡

SDCAS

/SSADS, SDRAS/SSOE, and SDWE/SSWE operate as SDCAS, SDRAS, and SDWE, respectively, during SDRAM accesses.

§

For the first write in a series of one or more consecutive adjacent writes, the write data is generated one CLKOUT2 cycle early to accommodate

the ED enable time.

ADVANCE INFORMATION