TMS320C6202

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS072B – AUGUST 1998 – REVISED AUGUST 1999

48

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

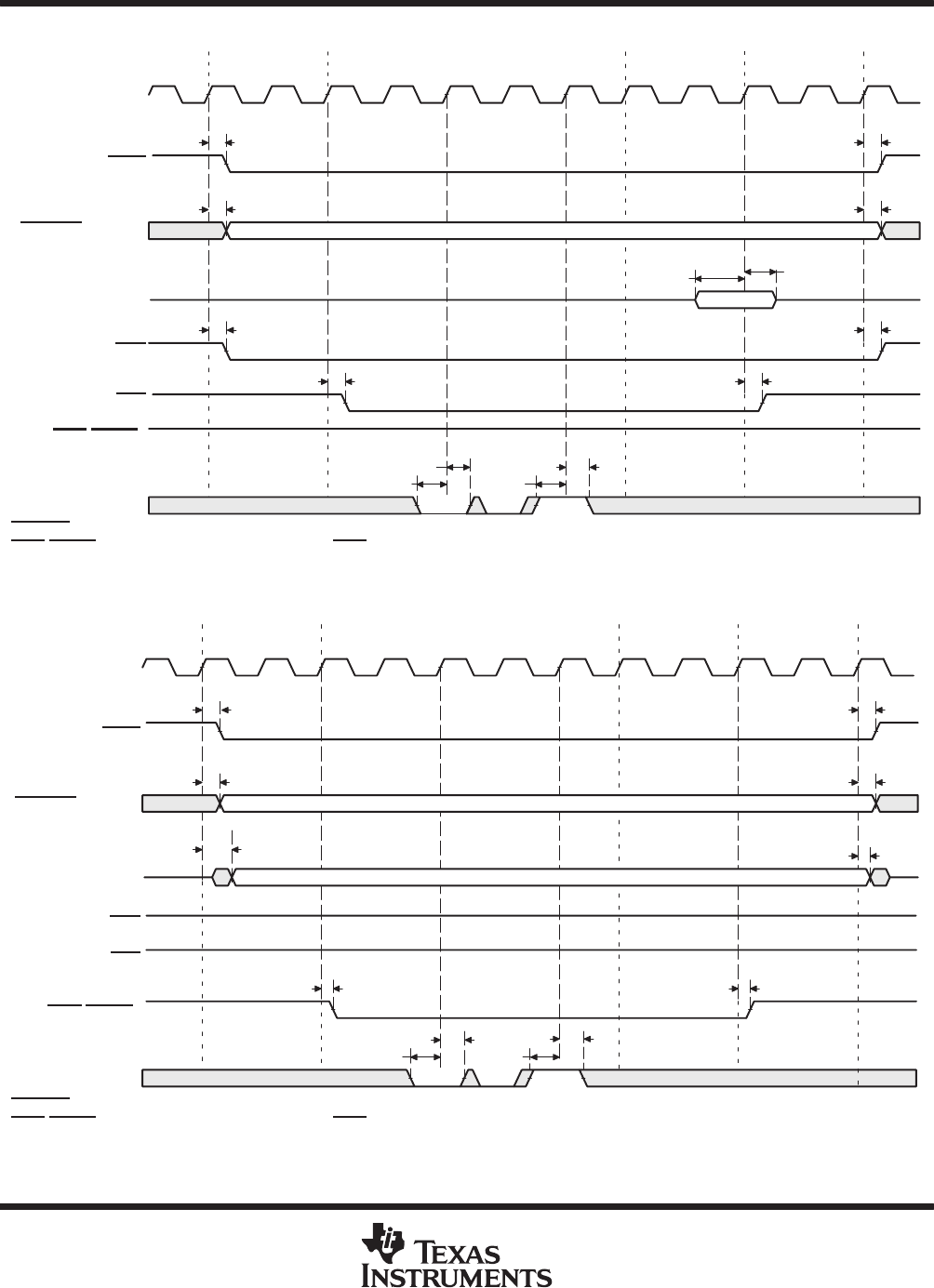

EXPANSION BUS ASYNCHRONOUS PERIPHERAL TIMING (CONTINUED)

99

8

8

77

66

5

4

32

11

CLKOUT1

XCEx

XBE[3:0]/XA[5:2]

†

XD[31:0]

XOE

XRE

XWE/XWAIT

‡

XRDY

§

Setup = 2 Strobe = 5

Not ready = 2

HOLD = 2

†

XBE[3:0]/XA[5:2] operates as address signals XA[5:2] during asynchronous peripheral accesses.

‡

XWE

/XWAIT operates as the write enable signal XWE during asynchronous peripheral accesses.

§

XRDY operates as active-high ready input during asynchronous peripheral accesses.

Figure 29. Expansion Bus Asynchronous Peripheral Read Timing

9

8

9

8

1212

11

10

32

11

CLKOUT1

XCEx

XBE[3:0]/XA[5:2]

†

XD[31:0]

XOE

XRE

XWE/XWAIT

‡

XRDY

§

Setup = 2 Strobe = 5

Not ready = 2

HOLD = 2

†

XBE[3:0]/XA[5:2] operates as address signals XA[5:2] during asynchronous peripheral accesses.

‡

XWE

/XWAIT operates as the write enable signal XWE during asynchronous peripheral accesses.

§

XRDY operates as active-high ready input during asynchronous peripheral accesses.

Figure 30. Expansion Bus Asynchronous Peripheral Write Timing

ADVANCE INFORMATION