TMS320C6202

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS072B – AUGUST 1998 – REVISED AUGUST 1999

15

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

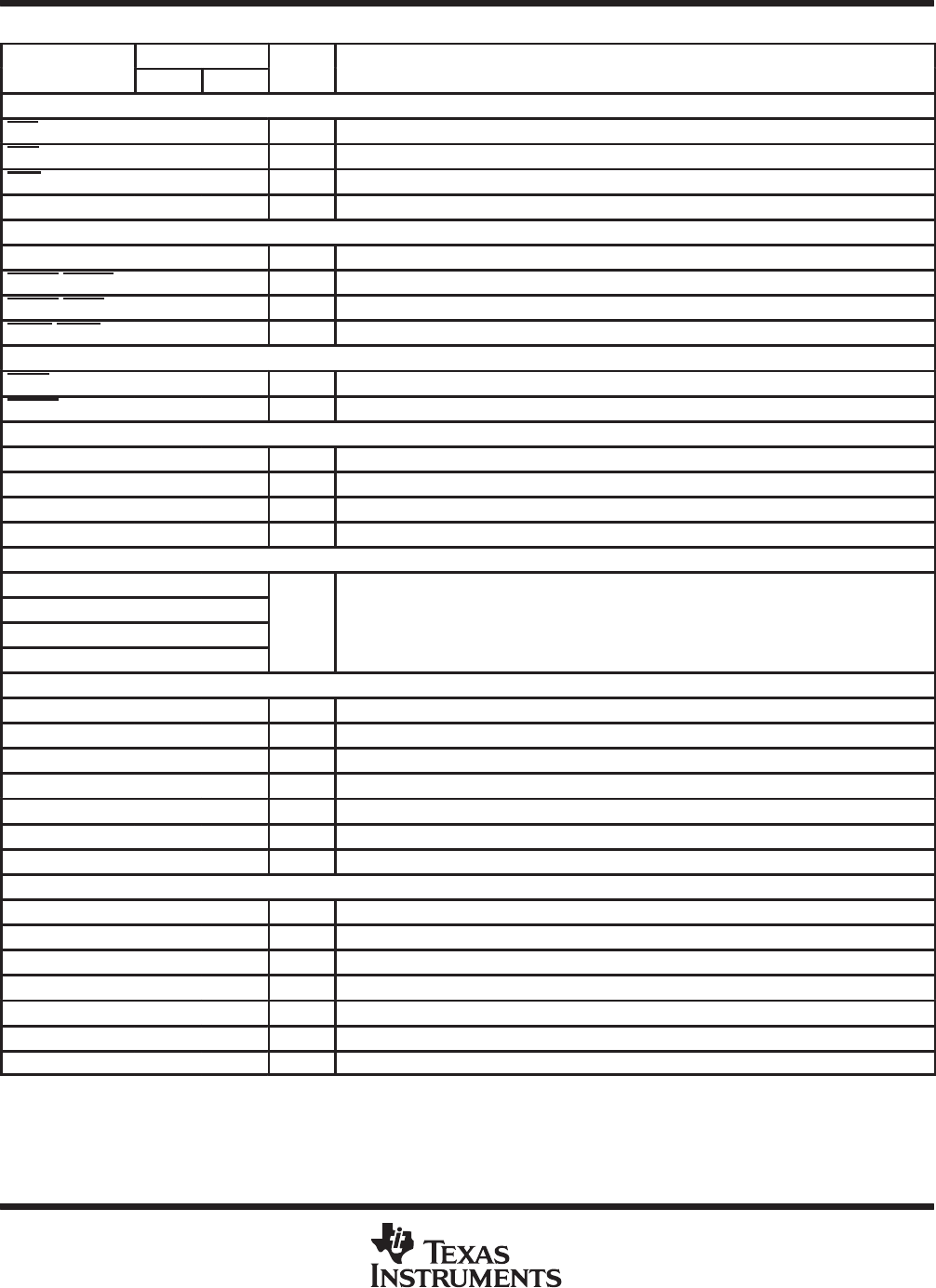

Signal Descriptions (Continued)

SIGNAL

PIN NO.

TYPE

†

DESCRIPTION

NAME

GJL GLS

TYPE

†

DESCRIPTION

EMIF – ASYNCHRONOUS MEMORY CONTROL

ARE V24 T21 O/Z Asynchronous memory read enable

AOE V25 R20 O/Z Asynchronous memory output enable

AWE U23 T22 O/Z Asynchronous memory write enable

ARDY W25 T20 I Asynchronous memory ready input

EMIF – SYNCHRONOUS DRAM (SDRAM)/SYNCHRONOUS BURST SRAM (SBSRAM) CONTROL

SDA10 AE21 AA19 O/Z SDRAM address 10 (separate for deactivate command)

SDCAS/SSADS AE22 AB21 O/Z SDRAM column-address strobe/SBSRAM address strobe

SDRAS/SSOE AF22 Y19 O/Z SDRAM row-address strobe/SBSRAM output enable

SDWE/SSWE AC20 AA20 O/Z SDRAM write enable/SBSRAM write enable

EMIF – BUS ARBITRATION

HOLD Y26 V22 I Hold request from the host

HOLDA V23 U21 O Hold-request-acknowledge to the host

TIMERS

TOUT1 J4 F2 O Timer 1 or general-purpose output

TINP1 G2 F3 I Timer 1 or general-purpose input

TOUT0 F1 D1 O Timer 0 or general-purpose output

TINP0 H4 E2 I Timer 0 or general-purpose input

DMA ACTION COMPLETE STATUS

DMAC3 Y3 V3

DMAC2 AA2 W2

O

DMA action com

p

lete

DMAC1 AB1 AA1

O

DMA

action

complete

DMAC0 AA3 W3

MULTICHANNEL BUFFERED SERIAL PORT 0 (McBSP0)

CLKS0 M4 K3 I External clock source (as opposed to internal)

CLKR0 M2 L2 I/O/Z Receive clock

CLKX0 M3 K1 I/O/Z Transmit clock

DR0 R2 M2 I Receive data

DX0 P4 M3 O/Z Transmit data

FSR0 N3 M1 I/O/Z Receive frame sync

FSX0 N4 L3 I/O/Z Transmit frame sync

MULTICHANNEL BUFFERED SERIAL PORT 1 (McBSP1)

CLKS1 G1 E1 I External clock source (as opposed to internal)

CLKR1 J3 G2 I/O/Z Receive clock

CLKX1 H2 G3 I/O/Z Transmit clock

DR1 L4 H1 I Receive data

DX1 J1 H2 O/Z Transmit data

FSR1 J2 H3 I/O/Z Receive frame sync

FSX1 K4 G1 I/O/Z Transmit frame sync

†

I = Input, O = Output, Z = High Impedance, S = Supply Voltage, GND = Ground

ADVANCE INFORMATION