TMS320C6202

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS072B – AUGUST 1998 – REVISED AUGUST 1999

32

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

INPUT AND OUTPUT CLOCKS (CONTINUED)

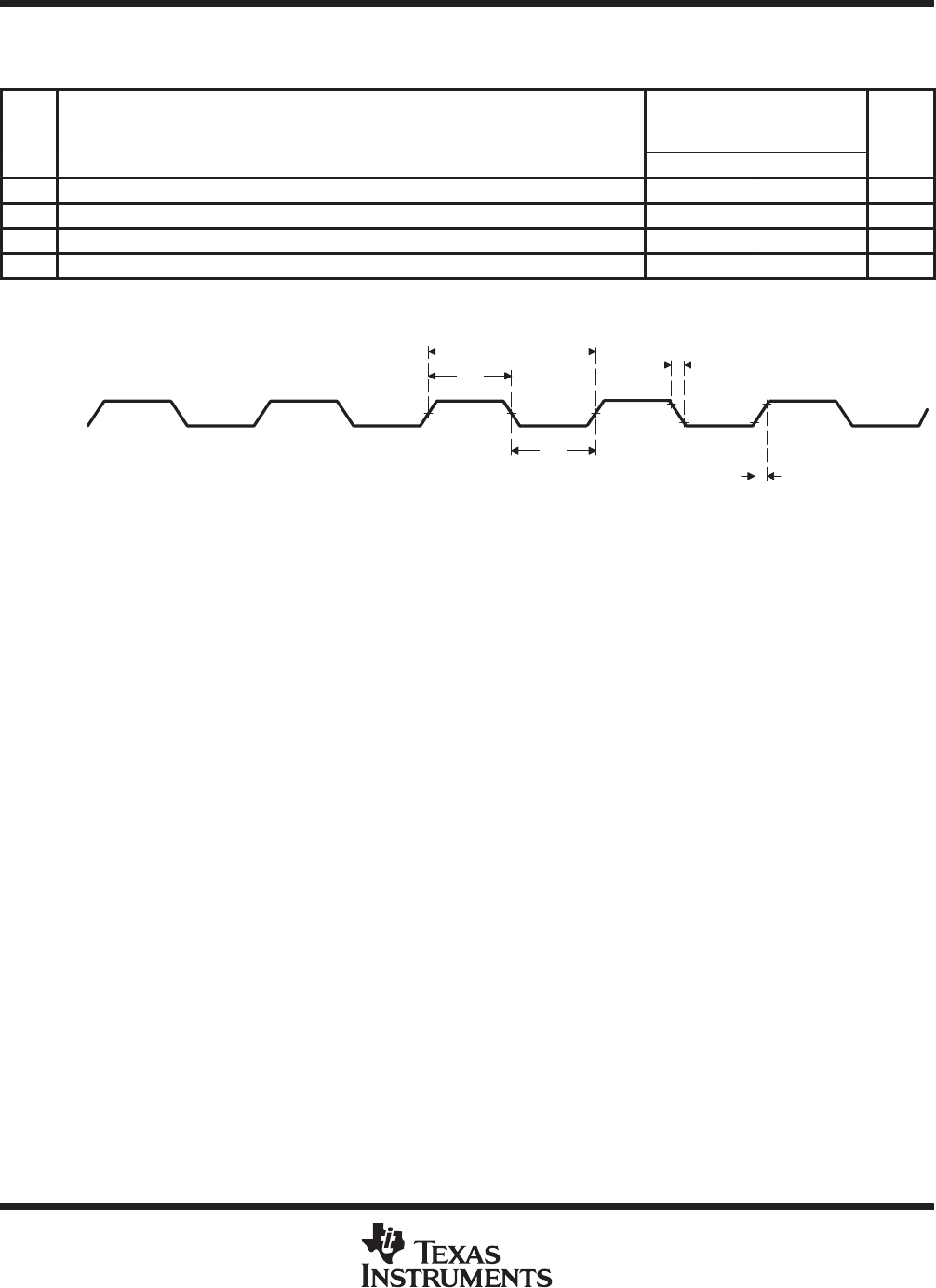

switching characteristics for XFCLK

†‡

(see Figure 12)

NO. PARAMETER

’C6202-200

’C6202-233

’C6202-250

UNIT

MIN MAX

1 t

c(XFCK)

Cycle time, XFCLK D * P – 0.7 D * P + 0.7 ns

2 t

w(XFCKH)

Pulse duration, XFCLK high (D/2) * P – 0.7 (D/2) * P + 0.7 ns

3 t

w(XFCKL)

Pulse duration, XFCLK low (D/2) * P – 0.7 (D/2) * P + 0.7 ns

4 t

t(XFCK)

Transition time, XFCLK 0.6 ns

†

P = 1/CPU clock frequency in ns.

‡

D = 8, 6, 4, or 2; FIFO clock divide ratio, user-programmable

XFCLK

1

2

3

4

4

Figure 12. XFCLK Timings

ADVANCE INFORMATION