TMS320C6202

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS072B – AUGUST 1998 – REVISED AUGUST 1999

59

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

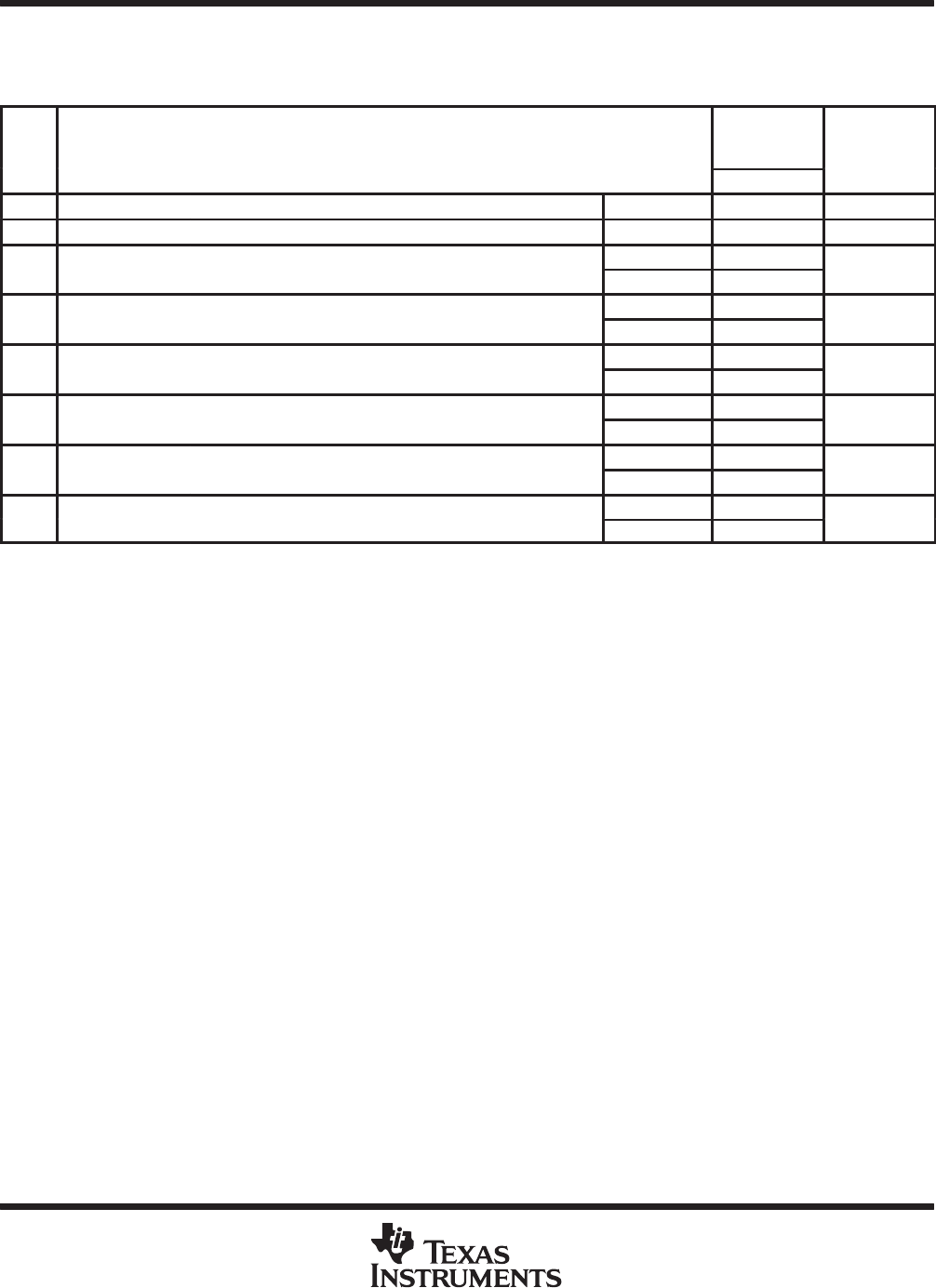

MULTICHANNEL BUFFERED SERIAL PORT TIMING

timing requirements for McBSP

†‡

(see Figure 40)

NO.

’C6202-200

’C6202-233

’C6202-250

UNIT

MIN MAX

2 t

c(CKRX)

Cycle time, CLKR/X CLKR/X ext 2P ns

3 t

w(CKRX)

Pulse duration, CLKR/X high or CLKR/X low CLKR/X ext P–1 ns

5

t

(FRH CKRL)

Setu

p

time external FSR high before CLKR low

CLKR int 9

ns

5

t

su(FRH-CKRL)

Set

u

p

time

,

e

x

ternal

FSR

high

before

CLKR

lo

w

CLKR ext

1

ns

6

t

h(CKRL FRH)

Hold time external FSR high after CLKR low

CLKR int 6

ns

6

t

h(CKRL-FRH)

Hold

time

,

e

x

ternal

FSR

high

after

CLKR

lo

w

CLKR ext

3

ns

7

t

(DRV CKRL)

Setu

p

time DR valid before CLKR low

CLKR int 8

ns

7

t

su(DRV-CKRL)

Set

u

p

time

,

DR

v

alid

before

CLKR

lo

w

CLKR ext

0

ns

8

t

h(CKRL DRV)

Hold time DR valid after CLKR low

CLKR int 3

ns

8

t

h(CKRL-DRV)

Hold

time

,

DR

v

alid

after

CLKR

lo

w

CLKR ext

3

ns

10

t

(FXH CKXL)

Setu

p

time external FSX high before CLKX low

CLKX int 9

ns

10

t

su(FXH-CKXL)

Set

u

p

time

,

e

x

ternal

FSX

high

before

CLKX

lo

w

CLKX ext

1

ns

11

t

h(CKXL FXH)

Hold time external FSX high after CLKX low

CLKX int 6

ns

11

t

h(CKXL-FXH)

Hold

time

,

e

x

ternal

FSX

high

after

CLKX

lo

w

CLKX ext 3

ns

†

CLKRP = CLKXP = FSRP = FSXP = 0. If polarity of any of the signals is inverted, then the timing references of that signal are also inverted.

‡

P = 1/CPU clock frequency in ns. For example, when running parts at 250 MHz, use P = 4 ns.

ADVANCE INFORMATION