TMS320C6202

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS072B – AUGUST 1998 – REVISED AUGUST 1999

54

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

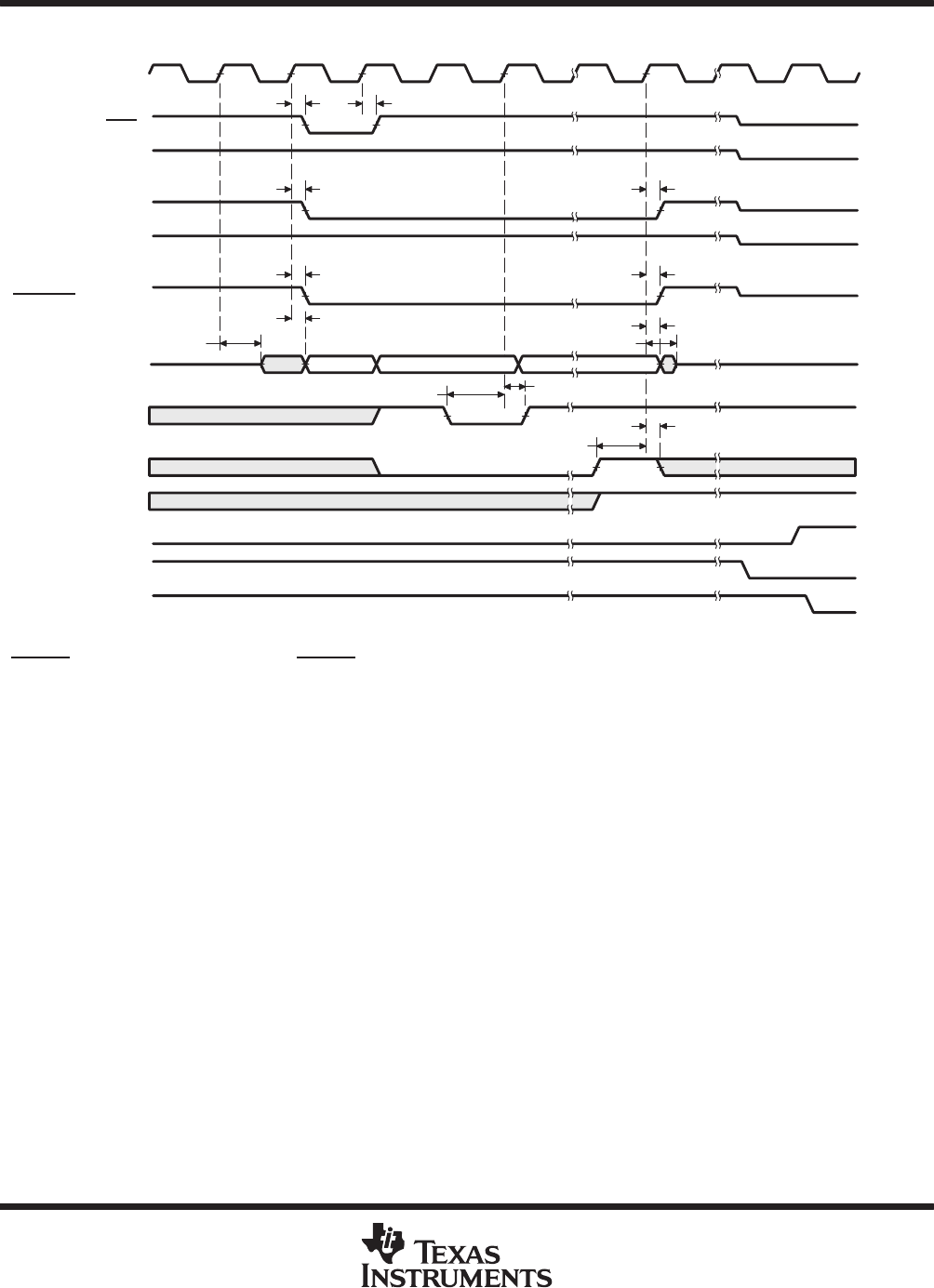

EXPANSION BUS SYNCHRONOUS HOST PORT TIMING (CONTINUED)

Addr D1 D2

15

14

12

11

8

7

6

5

44

22

11

XCLKIN

XAS

XW/R

†

XW/R

†

XBLAST

‡

XD[31:0]

XRDY

XBOFF

XHOLD

¶

XHOLDA

¶

XHOLD

#

XHOLDA

#

XBE[3:0]/XA[5:2]

§

†

XW/R input/output polarity selected at boot

‡

XBLAST output polarity is always active low.

§

XBE[3:0]

/XA[5:2] operates as byte enables XBE[3:0] during host-port accesses.

¶

Internal arbiter enabled

#

External arbiter enabled

||

This diagram illustrates XBOFF timing. Bus arbitration timing is shown in Figure 38 and Figure 39.

Figure 35. ’C6202 as Bus Master—BOFF Operation

||

ADVANCE INFORMATION