Chapter 18 CPU Baseboard: Description/Setting Configuration Jumpers

227

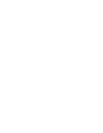

I/O Connector, J22: Rows A, B, & C (continued)

Signal Pin Signal Pin Signal Pin

X0D_L(1) A37 X0XRTS_L B37 X0HRTS_L C37

X0D_L(0) A38 GND B38 GND C38

GND A39 IGNNE_L B39 I2C_GLOBAL_SDA C39

NMI_5V A40 GND B40 SMI_L C40

I2C_BMC_SDA A41 BMC_SPI_BUS(3) B41 BMC_SPI_BUS(5) C41

I2C_BMC_SCL A42 GND B42 GND C42

BMC_SPI_BUS(0) A43 CPU_CPI_RESET_L B43 PROC_ RESET_L C43

BMC_SPI_BUS(6) A44 GND B44 A20M_L C44

BMC_SPI_BUS(1) A45 IO_TDI B45 PWRGDB C45

IO_TDO A46 GND B46 IO_TMS C46

IO_TCK A47 XIMB_ SOUT_ENT B47 SIN_TTL_ COM2 C47

COM2_TO_FP_EN A48 GND B48 GND C48

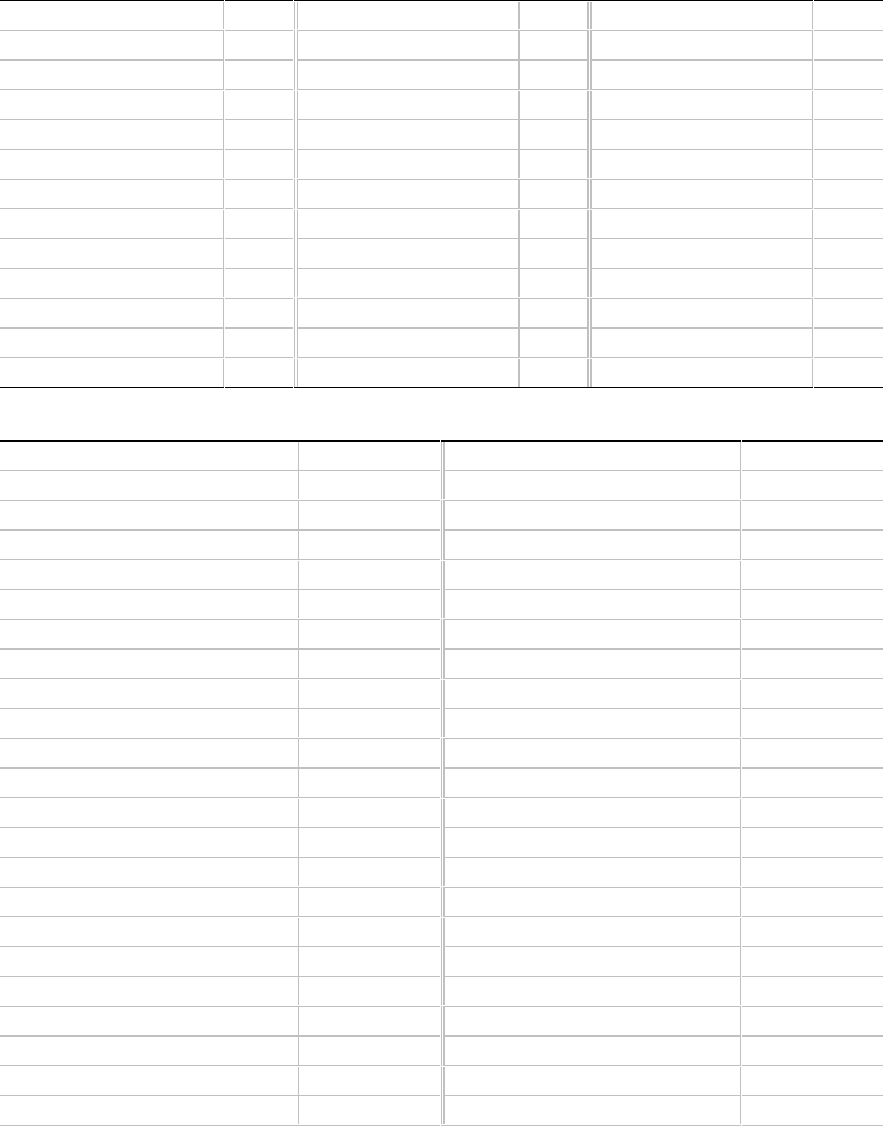

I/O Connector, J22: Rows D & E

Signal Pin Signal Pin

X1HSTBN_L D1 GND E1

X1HSTBP_L D2 GND E2

GND D3 GND E3

X1XSTBP_L D4 RESERVED E4

GND D5 GND E5

I2C_BACKUP_SDA D6 MIOC_INTREQ_L E6

GND D7 GND E7

I2C_BACKUP_SCL D8 X1RST_L E8

GND D9 GND E9

I2C_CEL_ CONNECT D10 X1BLK_L E10

GND D11 GND E11

PWR_CNTRL_RTC D12 I2C_CEL_ CONNECT_FPC E12

GND D13 GND E13

FP_NMI_SWT_L D14 PWR_CNTRL_SFC_L E14

PS_PWR_ON D15 GND E15

X1IB_L D16 PWR_GOOD E16

RESERVED D17 GND E17

FP_TO_PIIX4_PWR D18 SECURE_MODE_BMC E18

GND D19 GND E19

ISP_EN2_L D20 CPU_SLP_L E20

-12V D21 GND E21

ISP_FPC_EN_L D22 -12V E22

continued