www.ti.com

TMS320C6727,TMS320C6726,TMS320C6722

Floating-PointDigitalSignalProcessors

SPRS268E–MAY2005–REVISEDJANUARY2007

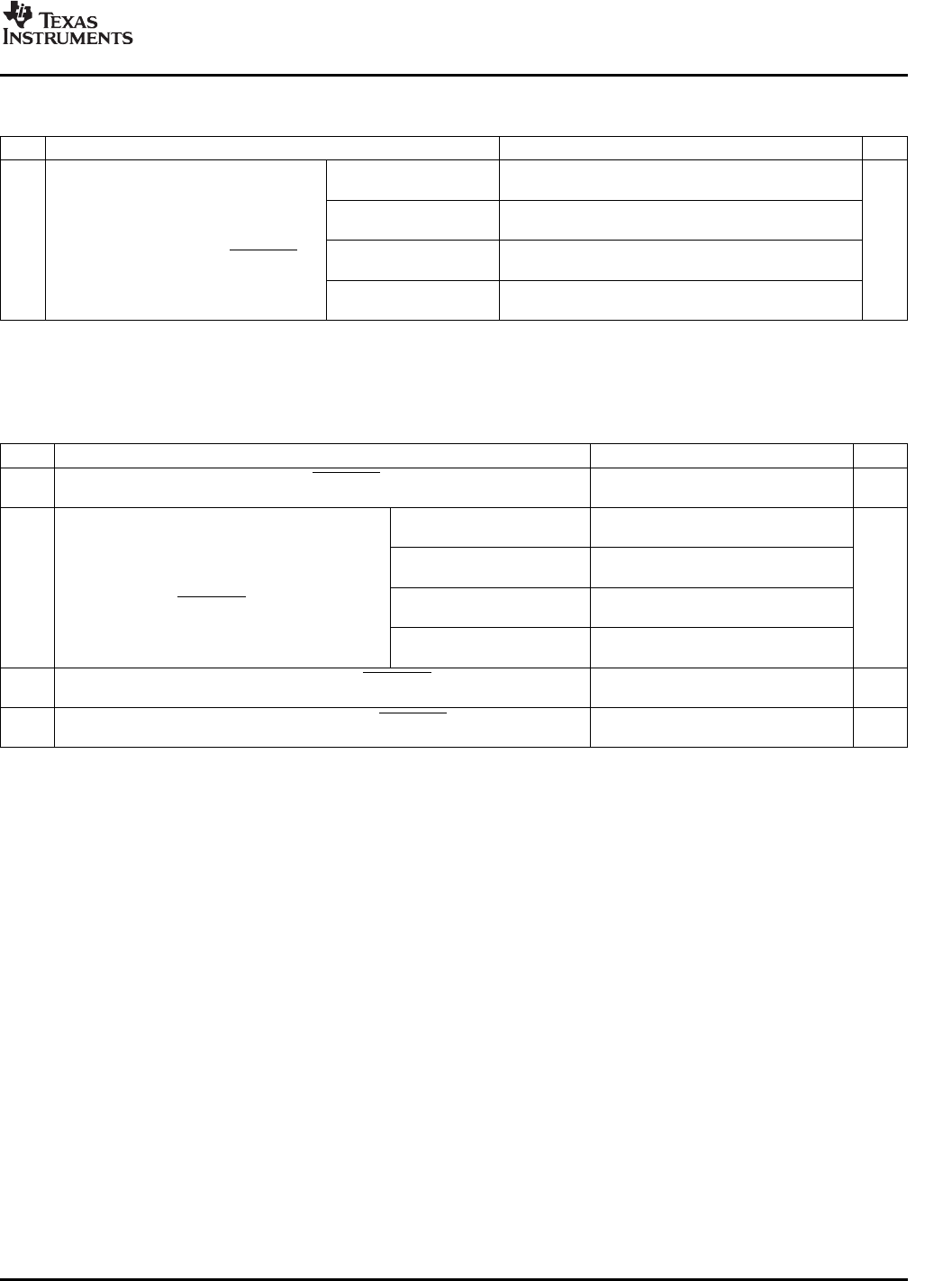

Table4-30.Additional

(1)

SPISlaveTimings,4-PinEnableOption

(2)(3)

NO.MINMAXUNIT

Polarity=0,Phase=0,

P–103P+15

fromSPIx_CLKfalling

Polarity=0,Phase=1,

0.5t

c(SPC)M

+P–100.5t

c(SPC)M

+3P+15

Delayfromfinal

fromSPIx_CLKfalling

24t

d(SPC_ENAH)S

SPIx_CLKedgetoslavens

Polarity=1,Phase=0,

deassertingSPIx_ENA.

P–103P+15

fromSPIx_CLKrising

Polarity=1,Phase=1,

0.5t

c(SPC)M

+P–100.5t

c(SPC)M

+3P+15

fromSPIx_CLKrising

(1)TheseparametersareinadditiontothegeneraltimingsforSPIslavemodes(Table4-26).

(2)P=SYSCLK2period

(3)FigureshowsonlyPolarity=0,Phase=0asanexample.Tablegivesparametersforallfourslaveclockingmodes.

Table4-31.Additional

(1)

SPISlaveTimings,4-PinChipSelectOption

(2)(3)

NO.MINMAXUNIT

RequireddelayfromSPIx_SCSassertedatslavetofirst

25t

d(SCSL_SPC)S

Pns

SPIx_CLKedgeatslave.

Polarity=0,Phase=0,

0.5t

c(SPC)M

+P+10

fromSPIx_CLKfalling

Polarity=0,Phase=1,

P+10

Requireddelayfromfinal

fromSPIx_CLKfalling

26t

d(SPC_SCSH)S

SPIx_CLKedgebeforens

Polarity=1,Phase=0,

SPIx_SCSisdeasserted.

0.5t

c(SPC)M

+P+10

fromSPIx_CLKrising

Polarity=1,Phase=1,

P+10

fromSPIx_CLKrising

DelayfrommasterassertingSPIx_SCStoslavedriving

27t

ena(SCSL_SOMI)S

P+15ns

SPIx_SOMIvalid

DelayfrommasterdeassertingSPIx_SCStoslave3-stating

28t

dis(SCSH_SOMI)S

P+15ns

SPIx_SOMI

(1)TheseparametersareinadditiontothegeneraltimingsforSPIslavemodes(Table4-26).

(2)P=SYSCLK2period

(3)FigureshowsonlyPolarity=0,Phase=0asanexample.Tablegivesparametersforallfourslaveclockingmodes.

SubmitDocumentationFeedbackPeripheralandElectricalSpecifications87