www.ti.com

TMS320C6727,TMS320C6726,TMS320C6722

Floating-PointDigitalSignalProcessors

SPRS268E–MAY2005–REVISEDJANUARY2007

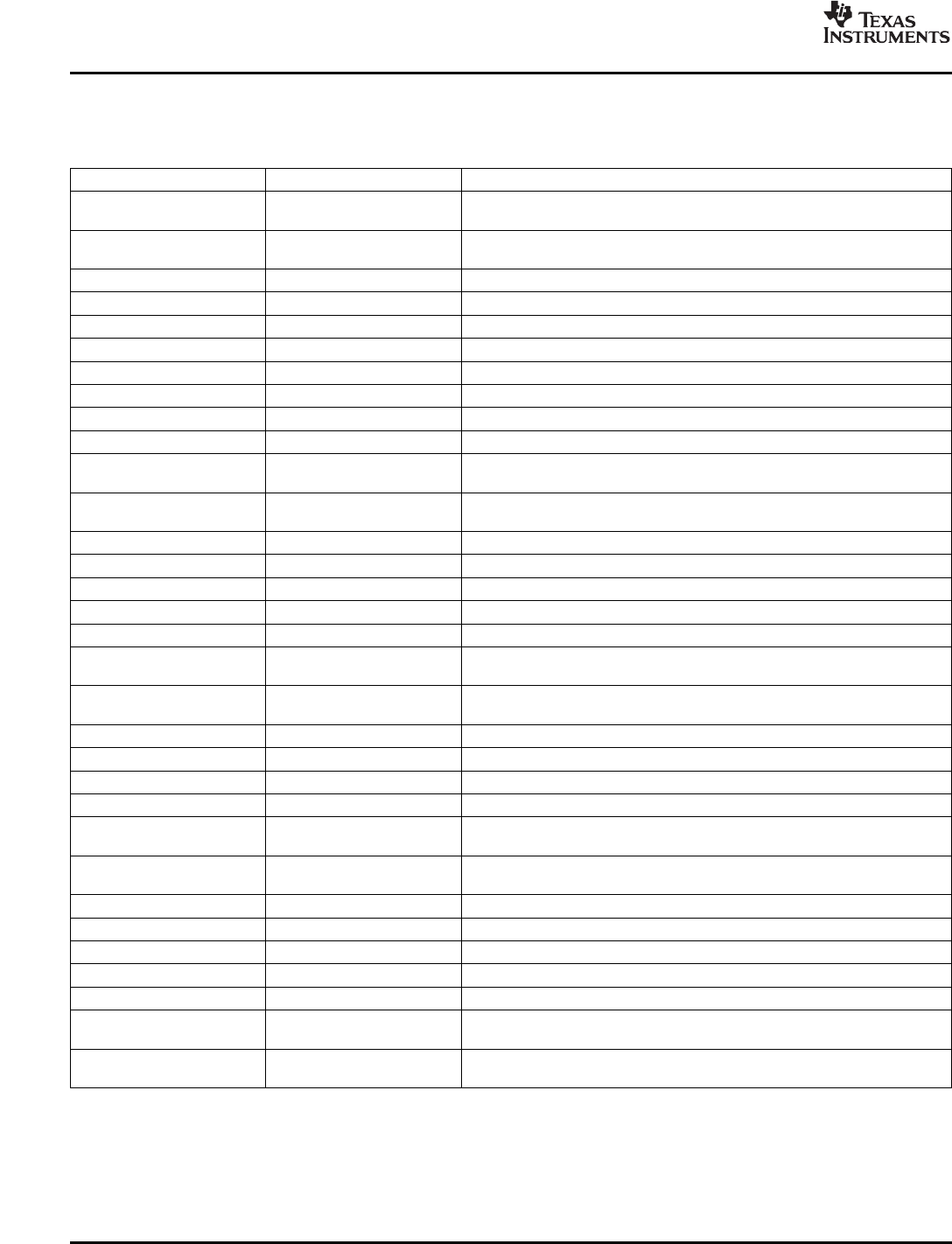

Table4-2listshowthesynchronizationeventsareassociatedwitheventnumbersinthedMAXcontroller.

Table4-2.dMAXPeripheralEventInputAssignments

EVENTNUMBEREVENTACRONYMEVENTDESCRIPTION

0DETR[0]TheCPUtriggerstheeventbycreatingappropriatetransition(edge)onbit0

inDETRregister.

1DETR[16]TheCPUtriggerstheeventbycreatingappropriatetransition(edge)onbit16

inDETRregister.

2RTIREQ0RTIDMAREQ[0]

3RTIREQ1RTIDMAREQ[1]

4MCASP0TXMcASP0TXDMAREQ

5MCASP0RXMcASP0RXDMAREQ

6MCASP1TXMcASP1TXDMAREQ

7MCASP1RXMcASP1RXDMAREQ

8MCASP2TXMcASP2TXDMAREQ

9MCASP2RXMcASP2RXDMAREQ

10DETR[1]TheCPUtriggerstheeventbycreatingappropriatetransition(edge)onbit1

inDETRregister.

11DETR[17]TheCPUtriggerstheeventbycreatingappropriatetransition(edge)onbit17

inDETRregister.

12UHPIINTUHPICPU_INT

13SPI0RXSPI0DMA_RX_REQ

14SPI1RXSPI1DMA_RX_REQ

15RTIREQ2RTIDMAREQ[2]

16RTIREQ3RTIDMAREQ[3]

17DETR[2]TheCPUtriggerstheeventbycreatingappropriatetransition(edge)onbit2

inDETRregister.

18DETR[18]TheCPUtriggerstheeventbycreatingappropriatetransition(edge)onbit18

inDETRregister.

19I2C0XEVTI2C0TransmitEvent

20I2C0REVTI2C0ReceiveEvent

21I2C1XEVTI2C1TransmitEvent

22I2C1REVTI2C1ReceiveEvent

23DETR[3]TheCPUtriggerstheeventbycreatingappropriatetransition(edge)onbit3

inDETRregister.

24DETR[19]TheCPUtriggerstheeventbycreatingappropriatetransition(edge)onbit19

inDETRregister.

25Reserved

26MCASP0ERRAMUTEIN0orMcASP0TXINTorMcASP0RXINT(erroronMcASP0)

27MCASP1ERRAMUTEIN1orMcASP1TXINTorMcASP1RXINT(erroronMcASP1)

28MCASP2ERRAMUTEIN2orMcASP2TXINTorMcASP2RXINT(erroronMcASP2)

29OVLREQ[0/1]ErroronRTI

30DETR[20]TheCPUtriggerstheeventbycreatingappropriatetransition(edge)onbit20

inDETRregister.

31DETR[21]TheCPUtriggerstheeventbycreatingappropriatetransition(edge)onbit21

inDETRregister.

PeripheralandElectricalSpecifications 42SubmitDocumentationFeedback