www.ti.com

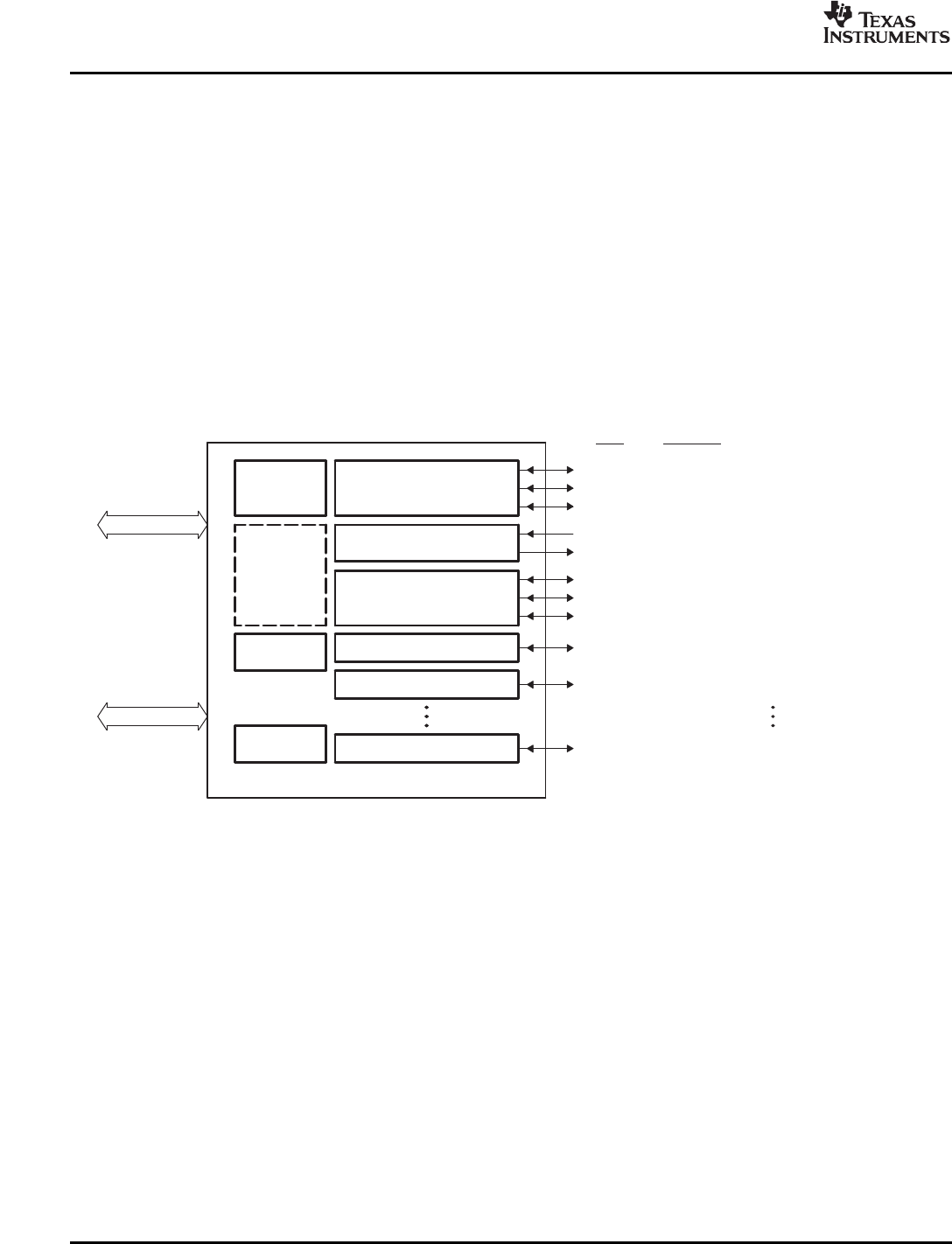

4.13MultichannelAudioSerialPorts(McASP0,McASP1,andMcASP2)

Receive Logic

Clock/Frame Generator

State Machine

Clock Check and

Serializer 0

Serializer 1

Serializer y

GIO

Control

DIT RAM

384 C

384 U

Optional

Transmit

Formatter

Receive

Formatter

Transmit Logic

Clock/Frame Generator

State Machine

McASPx (x = 0, 1, 2)

Peripheral

Configuration

Bus

McASP

DMA Bus

(Dedicated)

AHCLKRx

ACLKRx

AFSRx

AMUTEINx

AMUTEx

AFSXx

ACLKXx

AHCLKXx

AXRx[0]

AXRx[1]

AXRx[y]

Pins Function

Receive Master Clock

Receive Bit Clock

Receive Left/Right Clock or Frame Sync

Transmit Master Clock

Transmit Bit Clock

Transmit Left/Right Clock or Frame Sync

Transmit/Receive Serial Data Pin

Transmit/Receive Serial Data Pin

Transmit/Receive Serial Data Pin

Error Detection

The McASPs DO NOT have

dedicated AMUTEINx pins.

TMS320C6727,TMS320C6726,TMS320C6722

Floating-PointDigitalSignalProcessors

SPRS268E–MAY2005–REVISEDJANUARY2007

TheMcASPserialportisspecificallydesignedformultichannelaudioapplications.Itskeyfeaturesare:

•Flexibleclockandframesyncgenerationlogicandon-chipdividers

•Uptosixteentransmitorreceivedatapinsandserializers

•Largenumberofserialdataformatoptions,including:

–TDMFrameswith2to32timeslotsperframe(periodic)or1slotperframe(burst).

–Timeslotsof8,12,16,20,24,28,and32bits.

–Firstbitdelay0,1,or2clocks.

–MSBorLSBfirstbitorder.

–Left-orright-aligneddatawordswithintimeslots

•DITMode(optional)with384-bitChannelStatusand384-bitUserDataregisters.

•Extensiveerror-checkingandmutegenerationlogic

•AllunusedpinsGPIO-capable

Figure4-25.McASPBlockDiagram

PeripheralandElectricalSpecifications 68SubmitDocumentationFeedback