www.ti.com

8

7

4

4

3

2

21

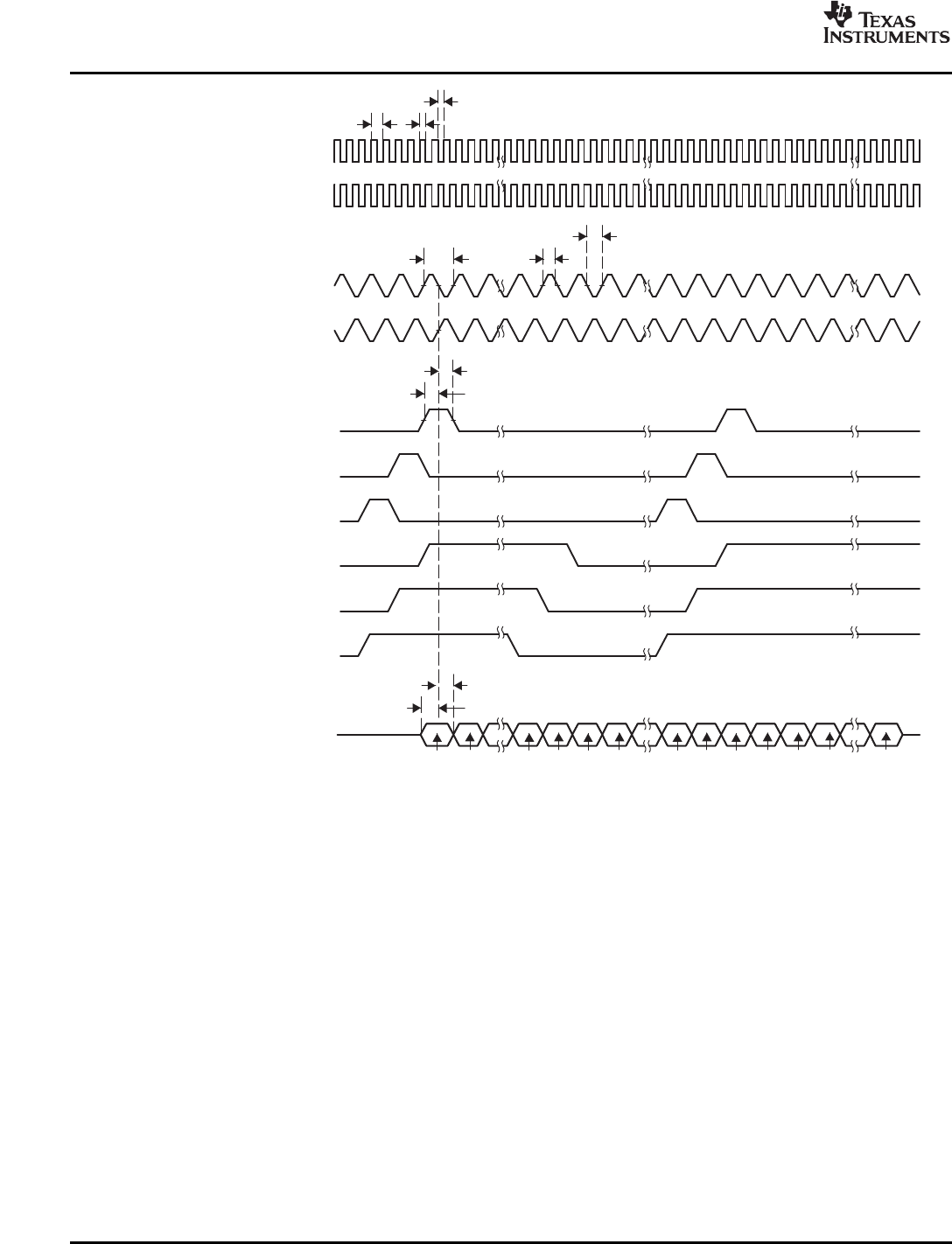

A0 A1 B0 B1A30 A31 B30 B31 C0 C1 C2 C3 C31

AHCLKR/X (Falling Edge Polarity)

AHCLKR/X (Rising Edge Polarity)

AFSR/X (Bit Width, 0 Bit Delay)

AFSR/X (Bit Width, 1 Bit Delay)

AFSR/X (Bit Width, 2 Bit Delay)

AFSR/X (Slot Width, 0 Bit Delay)

AFSR/X (Slot Width, 1 Bit Delay)

AFSR/X (Slot Width, 2 Bit Delay)

AXR[n] (Data In/Receive)

6

5

ACLKR/X (CLKRP = CLKXP = 0)

(A)

ACLKR/X (CLKRP = CLKXP = 1)

(B)

TMS320C6727,TMS320C6726,TMS320C6722

Floating-PointDigitalSignalProcessors

SPRS268E–MAY2005–REVISEDJANUARY2007

A.ForCLKRP=CLKXP=0,theMcASPtransmitterisconfiguredforrisingedge(toshiftdataout)andtheMcASP

receiverisconfiguredforfallingedge(toshiftdatain).

B.ForCLKRP=CLKXP=1,theMcASPtransmitterisconfiguredforfallingedge(toshiftdataout)andtheMcASP

receiverisconfiguredforrisingedge(toshiftdatain).

Figure4-29.McASPInputTimings

PeripheralandElectricalSpecifications 78SubmitDocumentationFeedback