www.ti.com

4.14SerialPeripheralInterfacePorts(SPI0,SPI1)

4.14.1SPIDevice-SpecificInformation

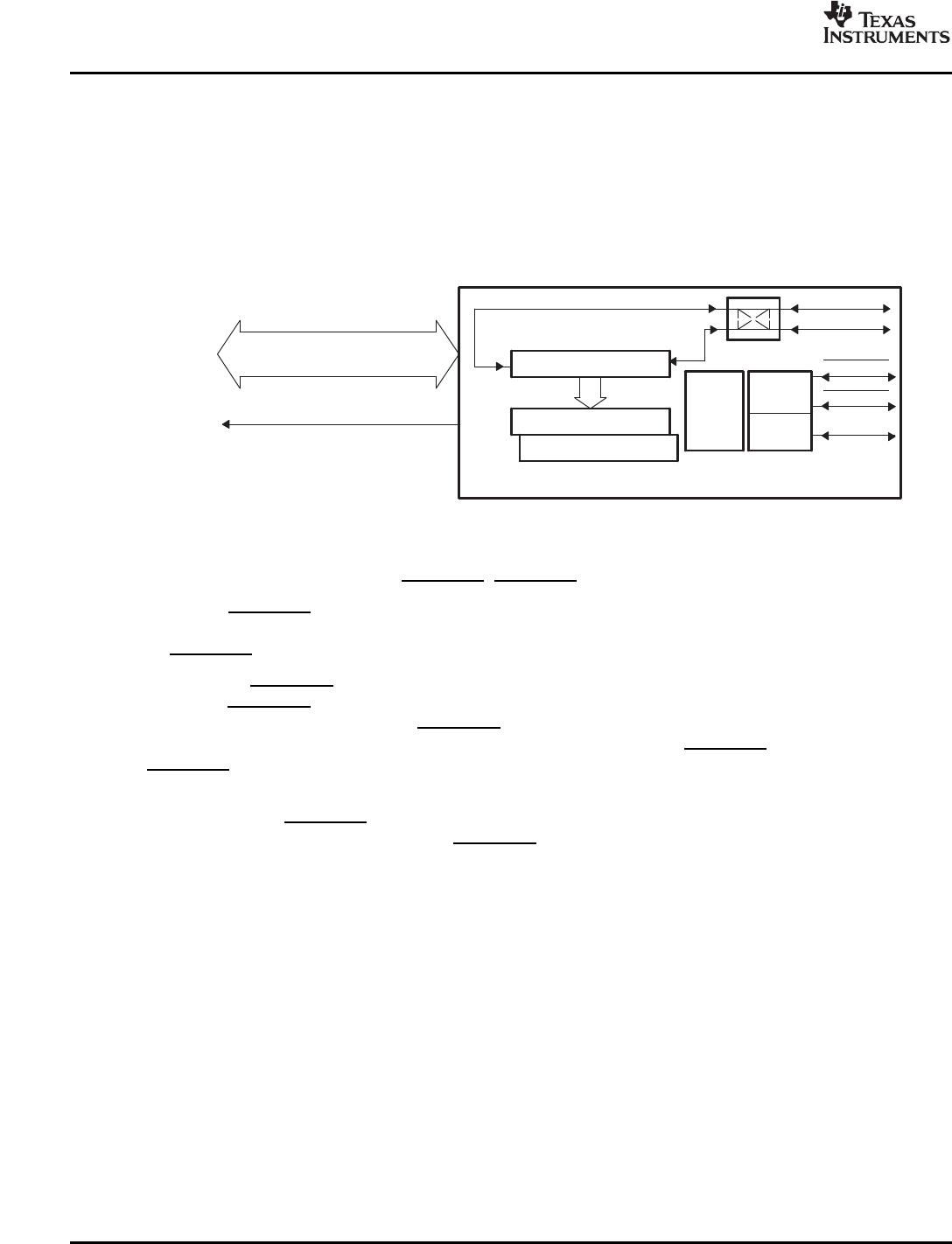

Peripheral

Configuration Bus

Interrupt and

DMA Requests

16-Bit Shift Register

16-Bit Buffer

16-Bit Emulation Buffer

C672x SPI Module

GPIO

Control

(all pins)

State

Machine

Clock

Control

SPIx_SIMO

SPIx_SOMI

SPIx_ENA

SPIx_SCS

SPIx_CLK

TMS320C6727,TMS320C6726,TMS320C6722

Floating-PointDigitalSignalProcessors

SPRS268E–MAY2005–REVISEDJANUARY2007

Figure4-31isablockdiagramoftheSPImodule,whichisasimpleshiftregisterandbufferpluscontrol

logic.Dataiswrittentotheshiftregisterbeforetransmissionoccursandisreadfromthebufferattheend

oftransmission.TheSPIcanoperateeitherasamaster,inwhichcase,itinitiatesatransferanddrives

theSPIx_CLKpin,orasaslave.Fourclockphaseandpolarityoptionsaresupportedaswellasmany

dataformattingoptions.

Figure4-31.BlockDiagramofSPIModule

TheSPIsupports3-,4-,and5-pinoperationwiththreebasicpins(SPIx_CLK,SPIx_SIMO,and

SPIx_SOMI)andtwooptionalpins(SPIx_SCS,SPIx_ENA).

TheoptionalSPIx_SCS(SlaveChipSelect)pinismostusefultoenableinslavemodewhenthereare

otherslavedevicesonthesameSPIport.TheC672xwillonlyshiftdataanddrivetheSPIx_SOMIpin

whenSPIx_SCSisheldlow.

Inslavemode,SPIx_ENAisanoptionaloutputandcanbedrivenineitherapush-pulloropen-drain

manner.TheSPIx_ENAoutputprovidesthestatusoftheinternaltransmitbuffer(SPIDAT0/1registers).In

four-pinmodewiththeenableoption,SPIx_ENAisassertedonlywhenthetransmitbufferisfull,indicating

thattheslaveisreadytobeginanothertransfer.Infive-pinmode,theSPIx_ENAisadditionallyqualified

bySPIx_SCSbeingasserted.Thisallowsasinglehandshakelinetobesharedbymultipleslavesonthe

sameSPIbus.

Inmastermode,theSPIx_ENApinisanoptionalinputandthemastercanbeconfiguredtodelaythestart

ofthenexttransferuntiltheslaveassertsSPIx_ENA.TheadditionofthishandshakesignalsimplifiesSPI

communicationsand,onaverage,increasesSPIbusthroughputsincethemasterdoesnotneedtodelay

eachtransferlongenoughtoallowfortheworst-caselatencyoftheslavedevice.Instead,eachtransfer

canbeginassoonasboththemasterandslavehaveactuallyservicedthepreviousSPItransfer.

PeripheralandElectricalSpecifications 80SubmitDocumentationFeedback