www.ti.com

TMS320C6727,TMS320C6726,TMS320C6722

Floating-PointDigitalSignalProcessors

SPRS268E–MAY2005–REVISEDJANUARY2007

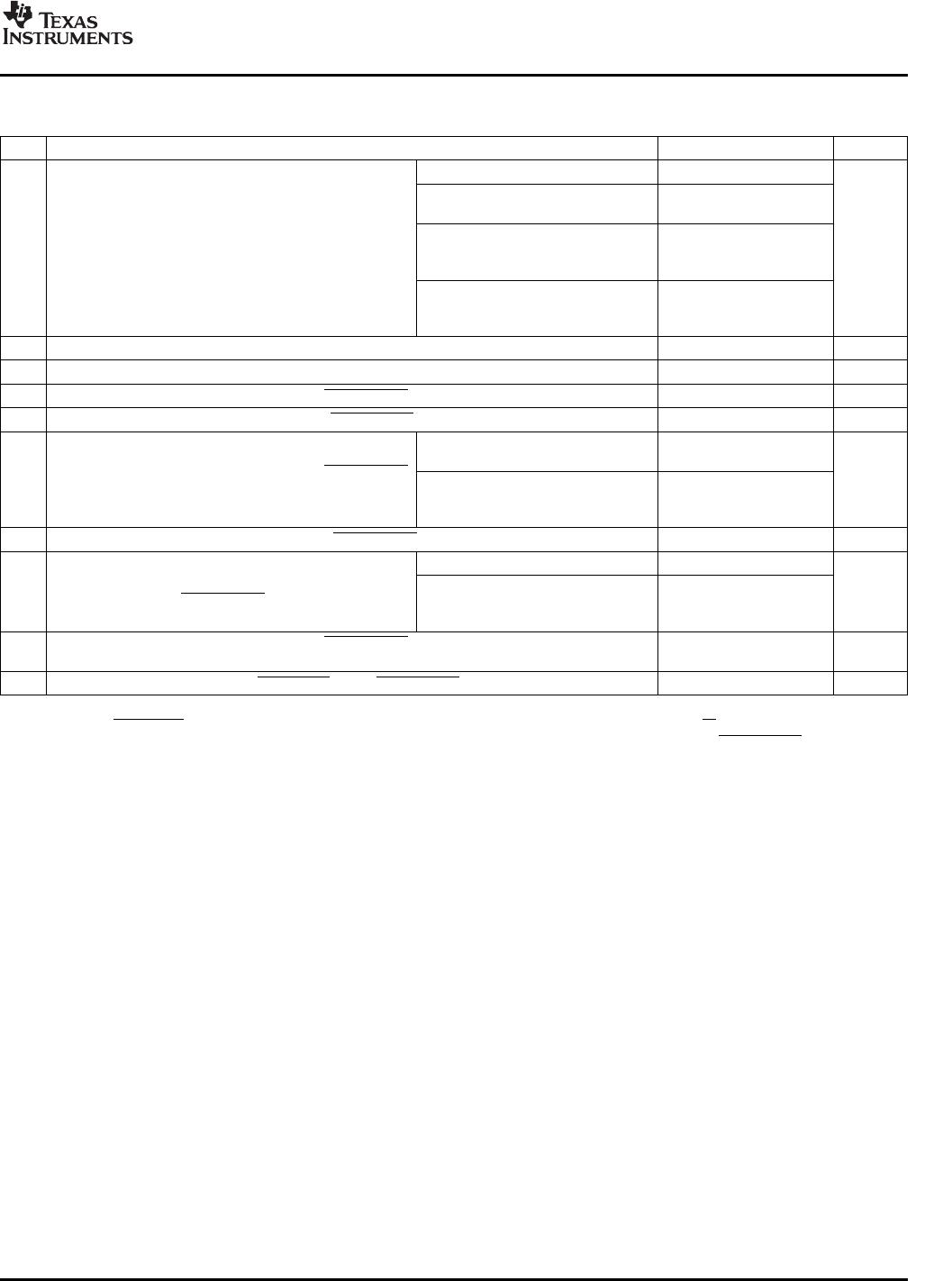

Table4-16.UHPIReadandWriteSwitchingCharacteristics

(1)(2)

NO.PARAMETERMINMAXUNIT

Case1.HPICorHPIAread115

Case2.HPIDreadwithno

9*2H+20

(3)

auto-increment

Case3.HPIDreadwith

1t

d(DSL-HDV)

Delaytime,DSlowtoHDvalidns

auto-incrementandreadFIFO9*2H+20

(3)

initiallyempty

Case4.HPIDreadwith

auto-incrementanddatapreviously115

prefetchedintothereadFIFO

2t

dis(DSH-HDV)

Disabletime,HDhigh-impedancefromDShigh14ns

3t

en(DSL-HDD)

Enabletime,HDdrivenfromDSlow315ns

4t

d(DSL-HRDYH)

Delaytime,DSlowtoUHPI_HRDYhigh12ns

5t

d(DSH-HRDYH)

Delaytime,DShightoUHPI_HRDYhigh12ns

Case1.HPIDreadwithno

10*2H+20

(3)

auto-increment

Delaytime,DSlowtoUHPI_HRDY

6t

d(DSL-HRDYL)

ns

Case2.HPIDreadwith

low

auto-incrementandreadFIFO10*2H+20

(3)

initialyempty

7t

d(HDV-HRDYL)

Delaytime,HDvalidtoUHPI_HRDYlow0ns

Case1.HPIAwrite5*2H+20

(3)

Delaytime,DShighto

Case2.HPIDreadwith

34t

d(DSH-HRDYL)

ns

UHPI_HRDYlow

auto-incrementandreadFIFO5*2H+20

(3)

initiallyempty

Delaytime,DSlowtoUHPI_HRDYlowforHPIAwriteandFIFOnot

35t

d(DSL-HRDYL)

40*2H+20

(3)

ns

empty

36t

d(HASL-HRDYH)

Delaytime,UHPI_HASlowtoUHPI_HRDYhigh12ns

(1)H=0.5*SYSCLK2period

(2)DSreferstoHSTROBE.HADreferstoUHPI_HCNTL[0],UHPI_HCNTL[1],UHPI_HHWIL,andUHPI_HRW.

(3)Maxdelayisabestcase,assumingnodelaysduetoresourceconflictsbetweenUHPIanddMAXorCPU.UHPI_HRDYshouldalways

beusedtoindicatewhenanaccessiscompleteinsteadofrelyingontheseparameters.

SubmitDocumentationFeedbackPeripheralandElectricalSpecifications63