www.ti.com

TMS320C6727,TMS320C6726,TMS320C6722

Floating-PointDigitalSignalProcessors

SPRS268E–MAY2005–REVISEDJANUARY2007

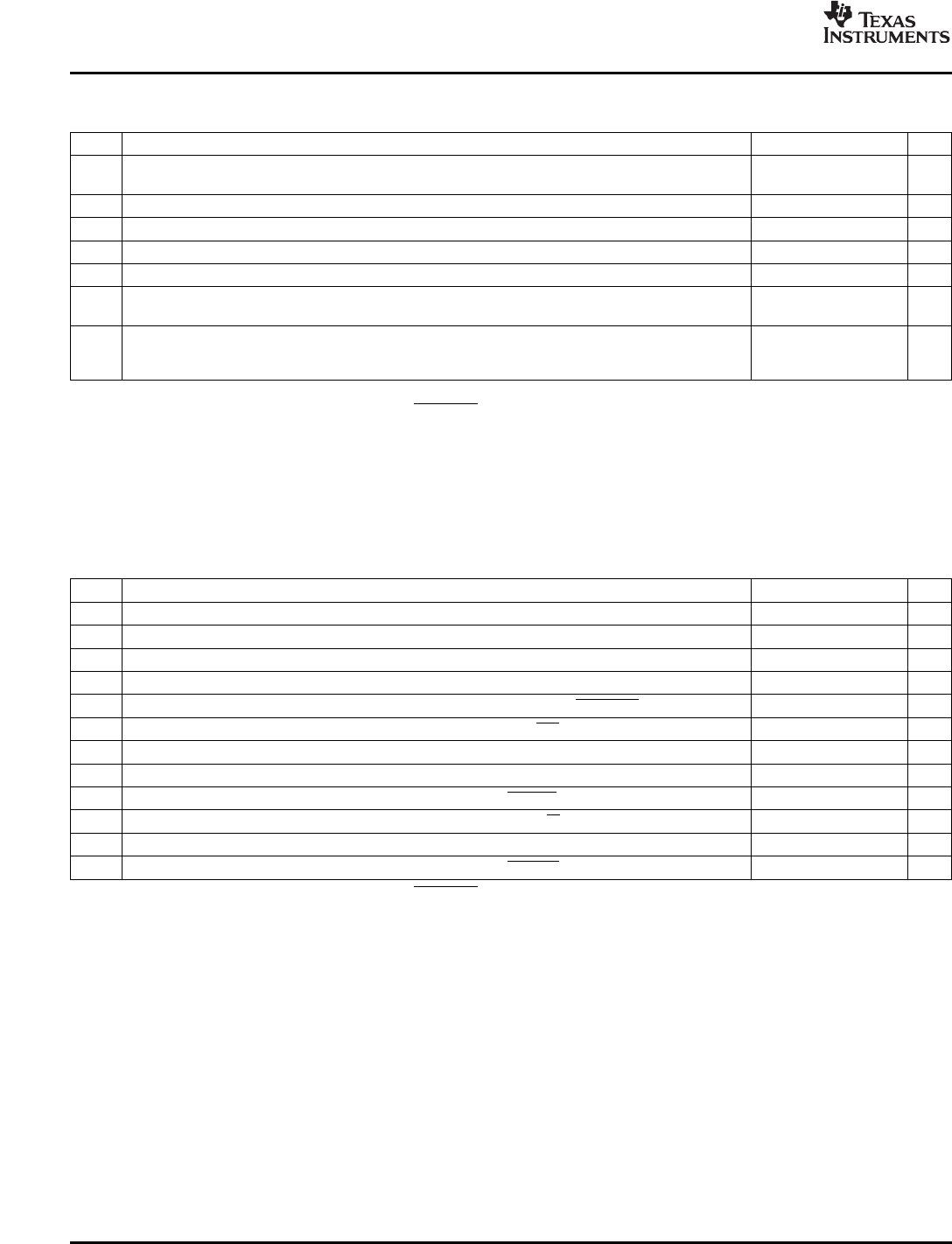

Table4-7.EMIFAsynchronousInterfaceTimingRequirements

(1)(2)

NO.MINMAXUNIT

Inputsetuptime,readdatavalidonEM_D[31:0]beforeEM_CLK

28t

su(EM_DV-EM_CLKH)A

5ns

rising

29t

h(EM_CLKH-EM_DIV)A

Inputholdtime,readdatavalidonEM_D[31:0]afterEM_CLKrising2ns

30t

su(EM_CLKH-EM_WAITV)A

Setuptime,EM_WAITvalidbeforeEM_CLKrisingedge5ns

31t

h(EM_CLKH-EM_WAITIV)A

Holdtime,EM_WAITvalidafterEM_CLKrisingedge0ns

33t

w(EM_WAIT)A

PulsewidthofEM_WAITassertionanddeassertion2E+5ns

DelayfromEM_WAITsampleddeassertedonEM_CLKrisingto

34t

d(EM_WAITD-HOLD)A

4E

(3)

ns

beginningofHOLDphase

SetupbeforeendofSTROBEphase(ifnoextendedwaitstatesare

35t

su(EM_WAITA-HOLD)A

inserted)bywhichEM_WAITmustbesampledassertedon4E

(3)

ns

EM_CLKrisinginordertoaddextendedwaitstates.

(4)

(1)E=SYSCLK3(EM_CLK)period.

(2)TheseparametersapplytomemoriesselectedbyEM_CS[2]inbothnormalandNANDmodes.

(3)TheseparametersspecifythenumberofEM_CLKcyclesoflatencybetweenEM_WAITbeingsampledatthedevicepinandtheEMIF

enteringtheHOLDphase.However,theasynchronoussetup(parameter30)andholdtime(parameter31)aroundeachEM_CLKedge

mustalsobemetinordertoensuretheEM_WAITsignaliscorrectlysampled.

(4)InFigure4-13,itappearsthattherearemorethan4EM_CLKcyclesencompassedbyparameter35.However,EM_CLKcyclesthatare

partoftheextendedwaitperiodshouldnotbecounted;the4EM_CLKrequirementistothestartofwheretheHOLDphasewould

beginiftherewerenoextendedwaitcycles.

Table4-8.EMIFAsynchronousInterfaceSwitchingCharacteristics

(1)

NO.PARAMETERMINMAXUNIT

1t

c(EM_CLK)

Cycletime,EMIFclockEM_CLK10ns

2t

w(EM_CLK)

Pulsewidth,highorlow,EMIFclockEM_CLK3ns

17t

dis(EM_CLKH-EM_DHZ)S

Delaytime,EM_CLKrisingtoEM_D[31:0]3-stated7.7ns

18t

ena(EM_CLKH-EM_DLZ)S

Outputholdtime,EM_CLKrisingtoEM_D[31:0]driving1.15ns

21t

d(EM_CLKH-EM_CS2V)A

Delaytime,fromEM_CLKrisingedgetoEM_CS[2]valid08ns

22t

d(EM_CLKH-EM_WE_DQMV)A

Delaytime,EM_CLKrisingtoEM_WE_DQM[3:0]valid08ns

23t

d(EM_CLKH-EM_AV)A

Delaytime,EM_CLKrisingtoEM_A[12:0]andEM_BA[1:0]valid08ns

24t

d(EM_CLKH-EM_DV)A

Delaytime,EM_CLKrisingtoEM_D[31:0]valid08ns

25t

d(EM_CLKH-EM_OEV)A

Delaytime,EM_CLKrisingtoEM_OEvalid08ns

26t

d(EM_CLKH-EM_RW)A

Delaytime,EM_CLKrisingtoEM_RWvalid08ns

27t

dis(EM_CLKH-EM_DDIS)A

Delaytime,EM_CLKrisingtoEM_D[31:0]3-stated08ns

32t

d(EM_CLKH-EM_WE)A

Delaytime,EM_CLKrisingtoEM_WEvalid08ns

(1)TheseparametersapplytomemoriesselectedbyEM_CS[2]inbothnormalandNANDmodes.

PeripheralandElectricalSpecifications 50SubmitDocumentationFeedback