www.ti.com

4.13.1McASPPeripheralRegistersDescription(s)

TMS320C6727,TMS320C6726,TMS320C6722

Floating-PointDigitalSignalProcessors

SPRS268E–MAY2005–REVISEDJANUARY2007

Table4-18isalistoftheMcASPregisters.Formoreinformationabouttheseregisters,seethe

TMS320C672xDSPMultichannelAudioSerialPort(McASP)ReferenceGuide(literaturenumber

SPRU878).

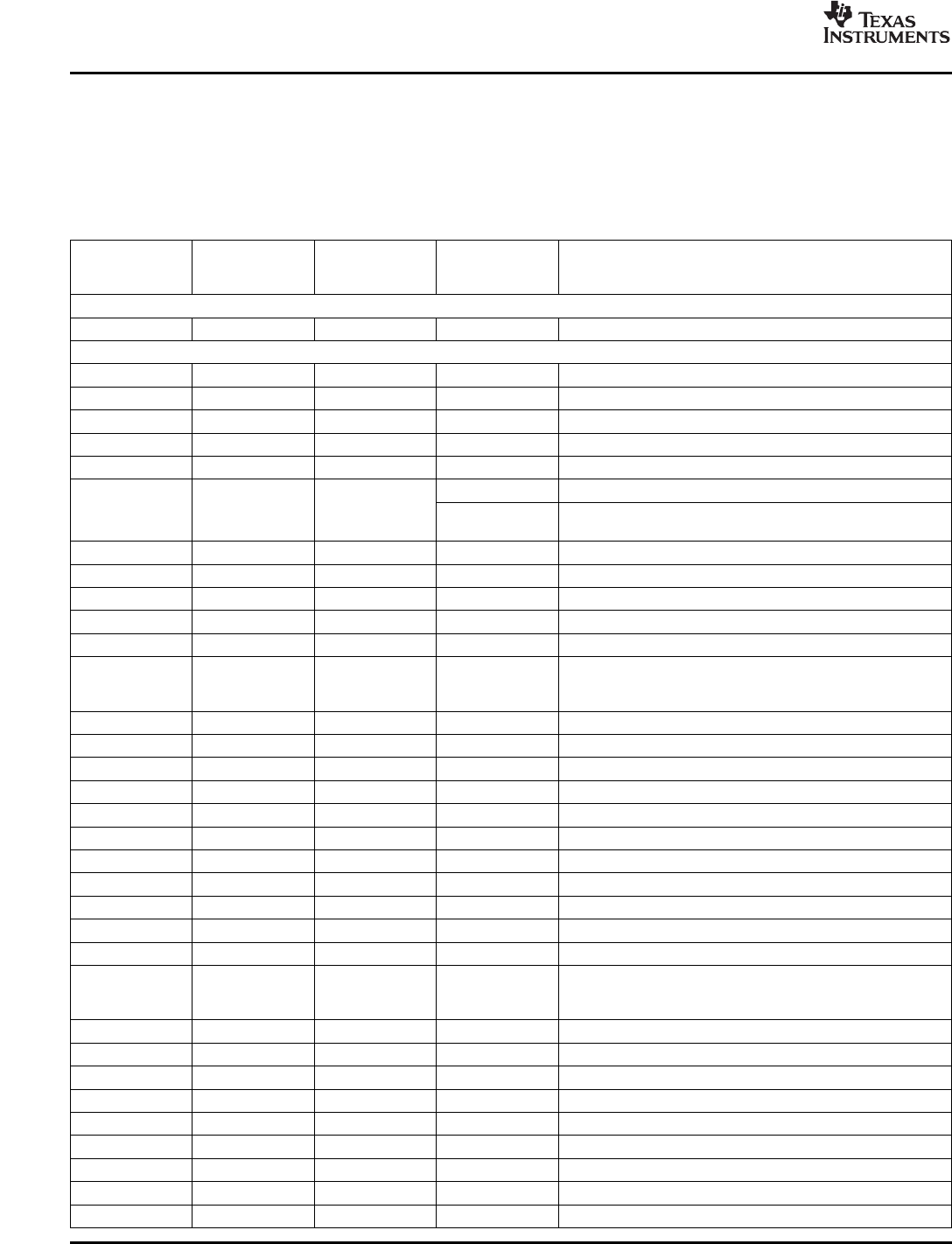

Table4-18.McASPRegistersAccessedThroughPeripheralConfigurationBus

McASP0McASP1McASP2

REGISTER

BYTEBYTEBYTEDESCRIPTION

NAME

ADDRESSADDRESSADDRESS

Device-LevelConfigurationRegistersControllingMcASP

0x400000180x4000001C0x40000020CFGMCASPxSelectstheperipheralpintobeusedasAMUTEINx

McASPInternalRegisters

0x440000000x450000000x46000000PIDPeripheralidentificationregister

0x440000040x450000040x46000004PWRDEMUPowerdownandemulationmanagementregister

0x440000100x450000100x46000010PFUNCPinfunctionregister

0x440000140x450000140x46000014PDIRPindirectionregister

0x440000180x450000180x46000018PDOUTPindataoutputregister

0x4400001C0x4500001C0x4600001CPDIN(reads)Readreturns:Pindatainputregister

PDSET(writes)Writesaffect:Pindatasetregister

(alternatewriteaddress:PDOUT)

0x440000200x450000200x46000020PDCLRPindataclearregister(alternatewriteaddress:PDOUT)

0x440000440x450000440x46000044GBLCTLGlobalcontrolregister

0x440000480x450000480x46000048AMUTEAudiomutecontrolregister

0x4400004C0x4500004C0x4600004CDLBCTLDigitalloopbackcontrolregister

0x440000500x450000500x46000050DITCTLDITmodecontrolregister

0x440000600x450000600x46000060RGBLCTLReceiverglobalcontrolregister:AliasofGBLCTL,only

receivebitsareaffected-allowsreceivertobereset

independentlyfromtransmitter

0x440000640x450000640x46000064RMASKReceiveformatunitbitmaskregister

0x440000680x450000680x46000068RFMTReceivebitstreamformatregister

0x4400006C0x4500006C0x4600006CAFSRCTLReceiveframesynccontrolregister

0x440000700x450000700x46000070ACLKRCTLReceiveclockcontrolregister

0x440000740x450000740x46000074AHCLKRCTLReceivehigh-frequencyclockcontrolregister

0x440000780x450000780x46000078RTDMReceiveTDMtimeslot0-31register

0x4400007C0x4500007C0x4600007CRINTCTLReceiverinterruptcontrolregister

0x440000800x450000800x46000080RSTATReceiverstatusregister

0x440000840x450000840x46000084RSLOTCurrentreceiveTDMtimeslotregister

0x440000880x450000880x46000088RCLKCHKReceiveclockcheckcontrolregister

0x4400008C0x4500008C0x4600008CREVTCTLReceiverDMAeventcontrolregister

0x440000A00x450000A00x460000A0XGBLCTLTransmitterglobalcontrolregister.AliasofGBLCTL,only

transmitbitsareaffected-allowstransmittertobereset

independentlyfromreceiver

0x440000A40x450000A40x460000A4XMASKTransmitformatunitbitmaskregister

0x440000A80x450000A80x460000A8XFMTTransmitbitstreamformatregister

0x440000AC0x450000AC0x460000ACAFSXCTLTransmitframesynccontrolregister

0x440000B00x450000B00x460000B0ACLKXCTLTransmitclockcontrolregister

0x440000B40x450000B40x460000B4AHCLKXCTLTransmithigh-frequencyclockcontrolregister

0x440000B80x450000B80x460000B8XTDMTransmitTDMtimeslot0-31register

0x440000BC0x450000BC0x460000BCXINTCTLTransmitterinterruptcontrolregister

0x440000C00x450000C00x460000C0XSTATTransmitterstatusregister

0x440000C40x450000C40x460000C4XSLOTCurrenttransmitTDMtimeslotregister

PeripheralandElectricalSpecifications 70SubmitDocumentationFeedback