www.ti.com

TMS320C6727,TMS320C6726,TMS320C6722

Floating-PointDigitalSignalProcessors

SPRS268E–MAY2005–REVISEDJANUARY2007

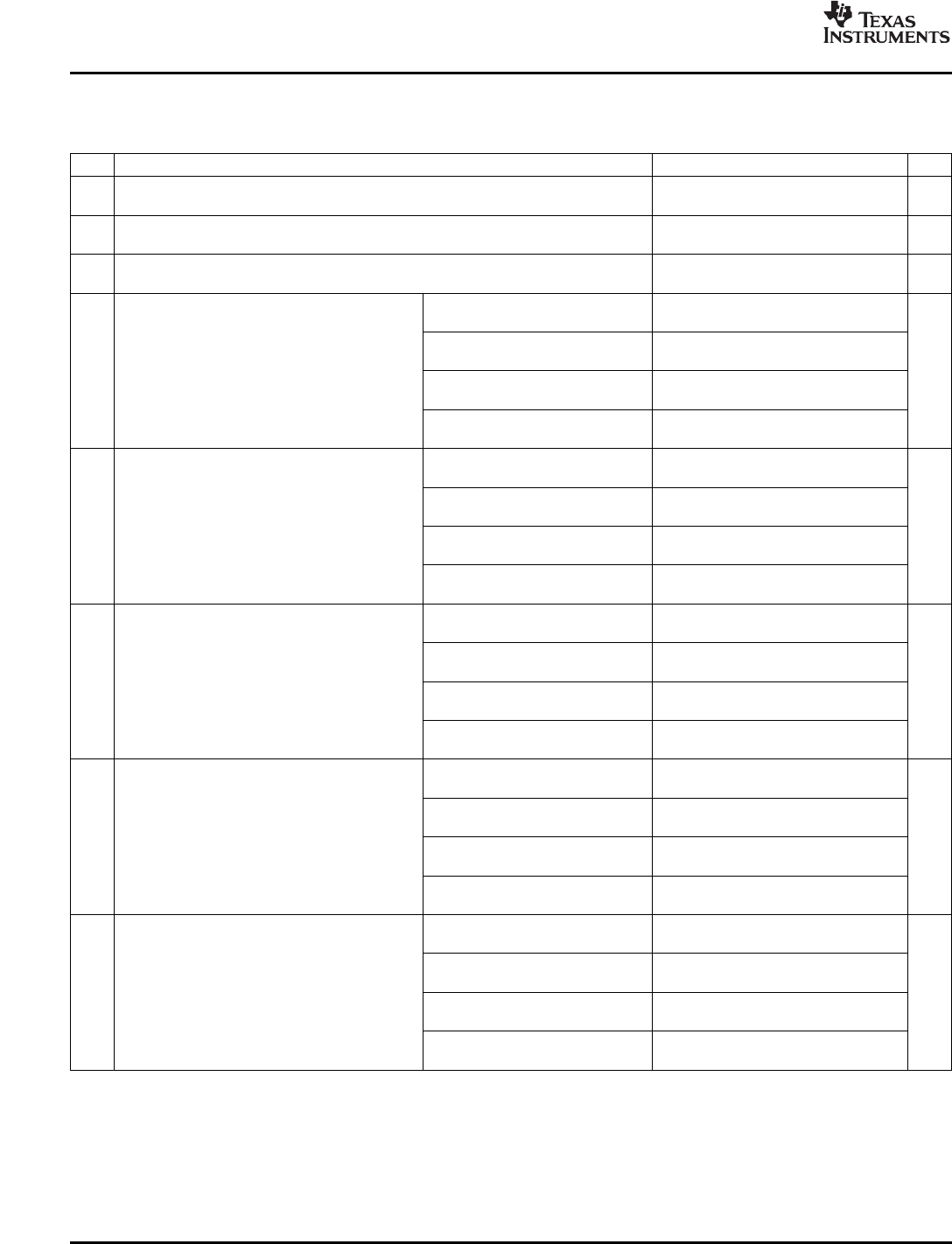

Table4-26.GeneralTimingRequirementsforSPIxSlaveModes

(1)

NO.MINMAXUNIT

greaterof8Por

9t

c(SPC)S

CycleTime,SPIx_CLK,AllSlaveModes256Pns

100ns

greaterof4Por

10t

w(SPCH)S

PulseWidthHigh,SPIx_CLK,AllSlaveModesns

45ns

greaterof4Por

11t

w(SPCL)S

PulseWidthLow,SPIx_CLK,AllSlaveModesns

45ns

Polarity=0,Phase=0,

2P

toSPIx_CLKrising

Setuptime,transmitdata

Polarity=0,Phase=1,

2P

writtentoSPIandoutput

toSPIx_CLKrising

12t

su(SOMI_SPC)S

ontoSPIx_SOMIpinbeforens

Polarity=1,Phase=0,

initialclockedgefrom

2P

toSPIx_CLKfalling

master.

(2)(3)

Polarity=1,Phase=1,

2P

toSPIx_CLKfalling

Polarity=0,Phase=0,

2P+15

fromSPIx_CLKrising

Polarity=0,Phase=1,

2P+15

Delay,subsequentbits

fromSPIx_CLKfalling

13t

d(SPC_SOMI)S

validonSPIx_SOMIafterns

Polarity=1,Phase=0,

transmitedgeofSPIx_CLK

2P+15

fromSPIx_CLKfalling

Polarity=1,Phase=1,

2P+15

fromSPIx_CLKrising

Polarity=0,Phase=0,

0.5t

c(SPC)S

–10

fromSPIx_CLKfalling

Polarity=0,Phase=1,

Outputholdtime,

0.5t

c(SPC)S

–10

fromSPIx_CLKrising

SPIx_SOMIvalidafter

14t

oh(SPC_SOMI)S

ns

receiveedgeofSPIxCLK,

Polarity=1,Phase=0,

0.5t

c(SPC)S

–10

exceptforfinalbit

(4)

fromSPIx_CLKrising

Polarity=1,Phase=1,

0.5t

c(SPC)S

–10

fromSPIx_CLKfalling

Polarity=0,Phase=0,

0.5P+15

toSPIx_CLKfalling

Polarity=0,Phase=1,

0.5P+15

InputSetupTime,

toSPIx_CLKrising

15t

su(SIMO_SPC)S

SPIx_SIMOvalidbeforens

Polarity=1,Phase=0,

receiveedgeofSPIx_CLK

0.5P+15

toSPIx_CLKrising

Polarity=1,Phase=1,

0.5P+15

toSPIx_CLKfalling

Polarity=0,Phase=0,

0.5P+5

fromSPIx_CLKfalling

Polarity=0,Phase=1,

0.5P+5

InputHoldTime,

fromSPIx_CLKrising

16t

ih(SPC_SIMO)S

SPIx_SIMOvalidafterns

Polarity=1,Phase=0,

receiveedgeofSPIx_CLK

0.5P+5

fromSPIx_CLKrising

Polarity=1,Phase=1,

0.5P+5

fromSPIx_CLKfalling

(1)P=SYSCLK2period

(2)FirstbitmaybeMSBorLSBdependinguponSPIconfiguration.SO(0)referstofirstbitandSO(n)referstolastbitoutputon

SPIx_SOMI.SI(0)referstothefirstbitinputandSI(n)referstothelastbitinputonSPIx_SIMO.

(3)MeasuredfromtheterminationofthewriteofnewdatatotheSPImodule,asevidencedbynewoutputdataappearingonthe

SPIx_SOMIpin.Inanalyzingthroughputrequirements,additionalinternalbuscyclesmustbeaccountedfortoallowdatatobewrittento

theSPImodulebyeithertheDSPCPUorthedMAX.

(4)ThefinaldatabitwillbeheldontheSPIx_SOMIpinuntiltheSPIDAT0orSPIDAT1registeriswrittenwithnewdata.

84PeripheralandElectricalSpecificationsSubmitDocumentationFeedback