www.ti.com

2.6High-PerformanceCrossbarSwitch

SYSCLK3

SYSCLK1 SYSCLK2

SYSCLK3

BR3 BR4

2 1

Priority

EMIF

External

Memory

SDRAM/

Flash

Priority

21 3 4

T2

SYSCLK2

SYSCLK1

BR1

SYSCLK2

SYSCLK1

BR2

Program

Master

Port

(PMP)

CPU

Slave

Port

(CSP)

Data

Master

Port

(DMP)

Memory Controller

M1 T1 M2

Priority

1 2 3

PLL SPI0 I2C0 I2C1RTI SPI1

Peripheral Configuration Bus

McASP2McASP1McASP0

McASP DMA Bus

Priority

1 2 3

Priority

1 2

T4

T3

dMAX MAX0 Unit Master Port − High Priority

dMAX MAX1 Unit Master Port − Second Priority

Memory Controller DMP − Data Read/Write by CPU

UHPI Master Interface (External Host CPU)

UHPI

Universal Host-Port

Interface

M5

MAX0 MAX1

1 2 3

Priority

Config

dMAX

T5M3 M4

External

Host MCU

Config

ROM RAM CPU

Program

Cache

Crossbar

TMS320C6727,TMS320C6726,TMS320C6722

Floating-PointDigitalSignalProcessors

SPRS268E–MAY2005–REVISEDJANUARY2007

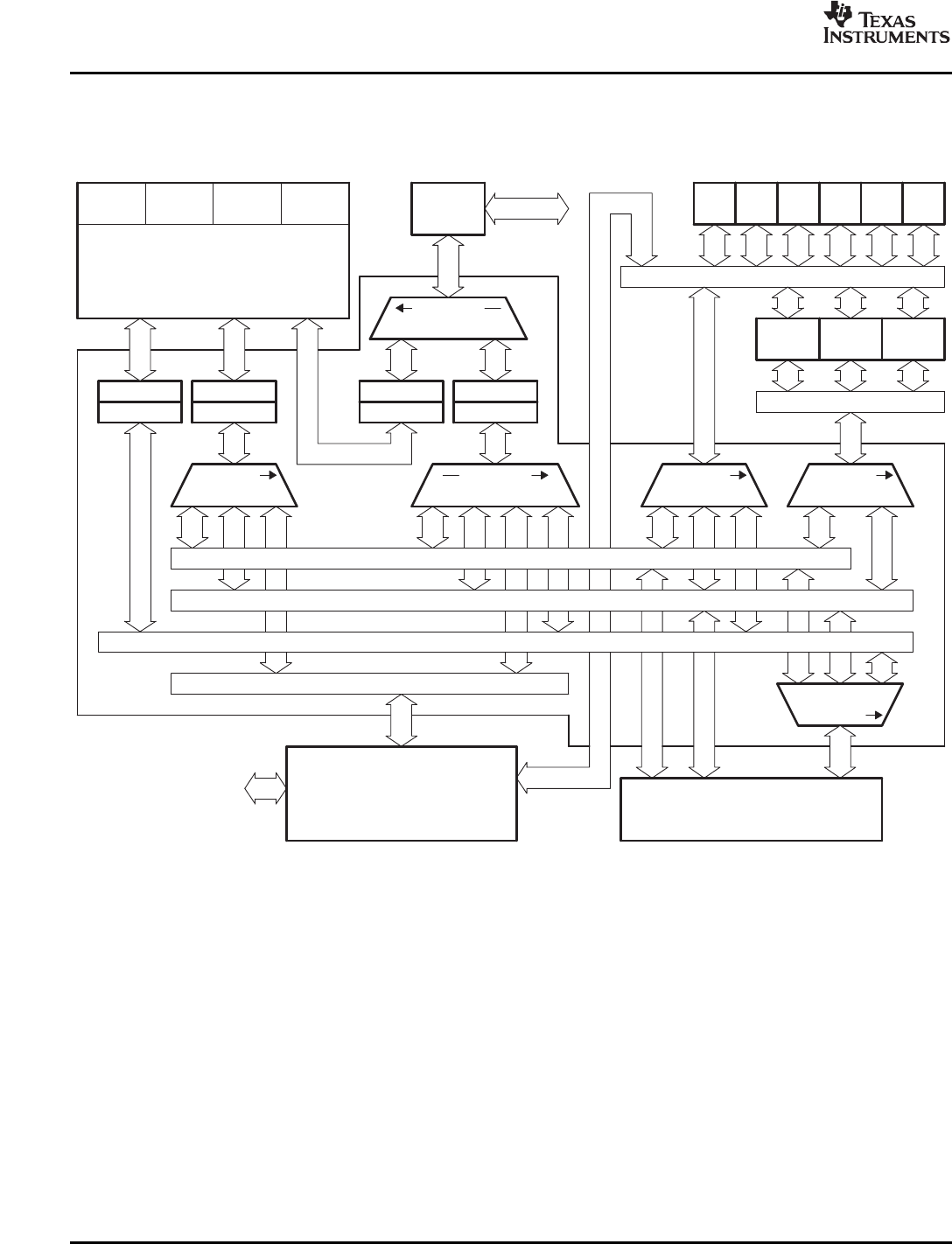

TheC672xDSPincludesahigh-performancecrossbarswitchthatactsasacentralhubbetweenbus

mastersandtargets.Figure2-4illustratestheconnectivityofthecrossbarswitch.

Figure2-4.BlockDiagramofCrossbarSwitch

AsshowninFigure2-4,therearefivebusmasters:

M1MemorycontrollerDMPforCPUdataaccessestoperipheralsandEMIF.

M2MemorycontrollerPMPforprogramcachefillsfromtheEMIF.

M3dMAXHiMAXmasterportforhigh-priorityDMAaccesses.

M4dMAXLoMAXmasterportforlower-priorityDMAaccesses.

M5UHPImasterportforanexternalMCUtoaccesson-chipandoff-chipmemories.

DeviceOverview 12SubmitDocumentationFeedback