www.ti.com

TMS320C6727,TMS320C6726,TMS320C6722

Floating-PointDigitalSignalProcessors

SPRS268E–MAY2005–REVISEDJANUARY2007

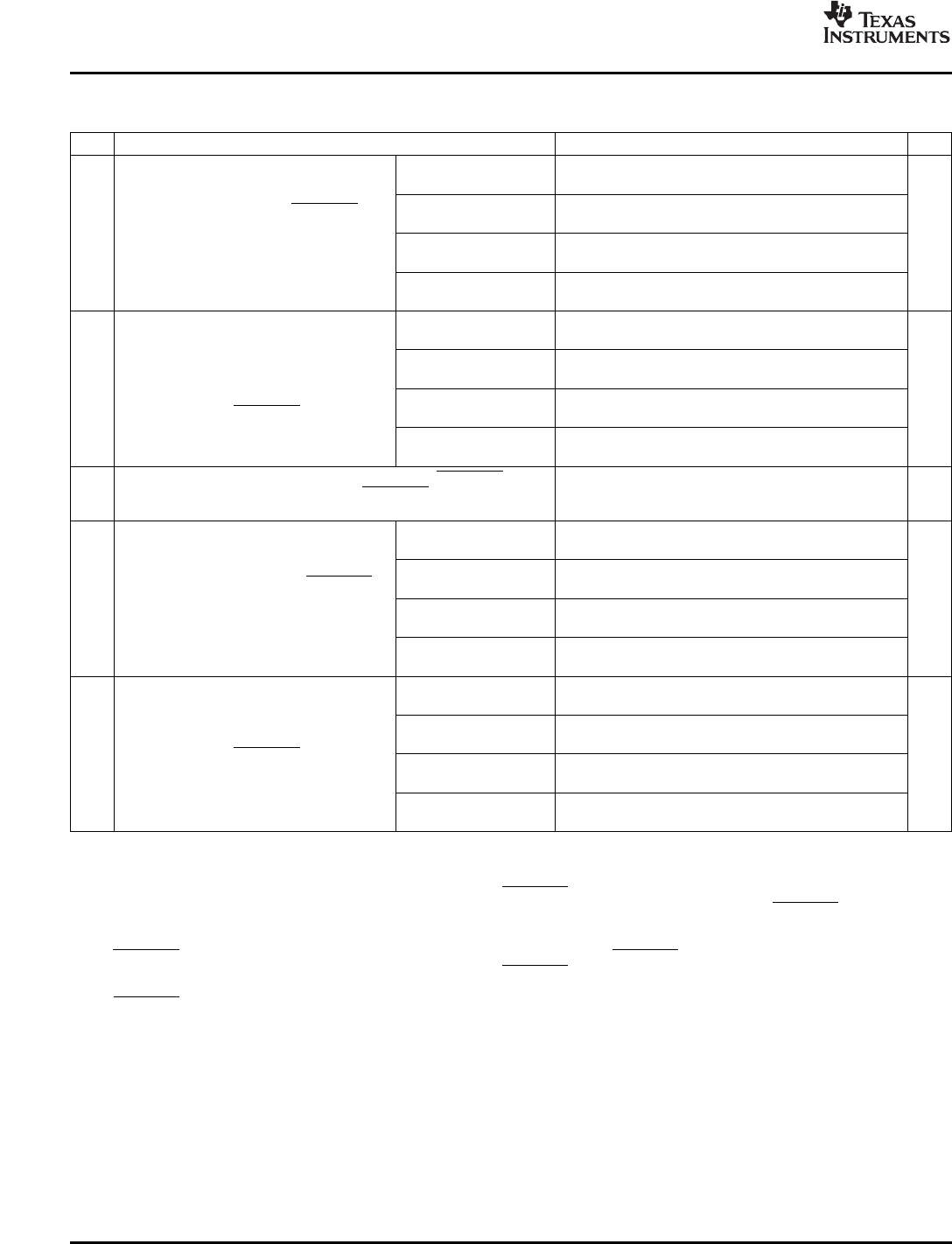

Table4-29.Additional

(1)

SPIMasterTimings,5-PinOption

(2)(3)

NO.MINMAXUNIT

Polarity=0,Phase=0,

0.5t

c(SPC)M

fromSPIx_CLKfalling

Maxdelayforslaveto

Polarity=0,Phase=1,

deassertSPIx_ENAafter

0

fromSPIx_CLKfalling

finalSPIx_CLKedgeto

18t

d(SPC_ENA)M

ns

ensuremasterdoesnot

Polarity=1,Phase=0,

0.5t

c(SPC)M

beginthenext

fromSPIx_CLKrising

transfer.

(4)

Polarity=1,Phase=1,

0

fromSPIx_CLKrising

Polarity=0,Phase=0,

0.5t

c(SPC)M

fromSPIx_CLKfalling

Polarity=0,Phase=1,

Delayfromfinal

0

fromSPIx_CLKfalling

SPIx_CLKedgeto

20t

d(SPC_SCS)M

ns

masterdeasserting

Polarity=1,Phase=0,

0.5t

c(SPC)M

SPIx_SCS

(5)(6)

fromSPIx_CLKrising

Polarity=1,Phase=1,

0

fromSPIx_CLKrising

MaxdelayforslaveSPItodriveSPIx_ENAvalid

21t

d(SCSL_ENAL)M

aftermasterassertsSPIx_SCStodelaythe0.5Pns

masterfrombeginningthenexttransfer.

Polarity=0,Phase=0,

2P–10

toSPIx_CLKrising

Polarity=0,Phase=1,

0.5t

c(SPC)M

+2P–10

DelayfromSPIx_SCS

toSPIx_CLKrising

22t

d(SCS_SPC)M

activetofirstns

Polarity=1,Phase=0,

SPIx_CLK

(7)(8)(9)

2P–10

toSPIx_CLKfalling

Polarity=1,Phase=1,

0.5t

c(SPC)M

+2P–10

toSPIx_CLKfalling

Polarity=0,Phase=0,

3P+15

toSPIx_CLKrising

Polarity=0,Phase=1,

0.5t

c(SPC)M

+3P+15

Delayfromassertionof

toSPIx_CLKrising

23t

d(ENA_SPC)M

SPIx_ENAlowtofirstns

Polarity=1,Phase=0,

SPIx_CLKedge.

(10)

3P+15

toSPIx_CLKfalling

Polarity=1,Phase=1,

0.5t

c(SPC)M

+3P+15

toSPIx_CLKfalling

(1)TheseparametersareinadditiontothegeneraltimingsforSPImastermodes(Table4-25).

(2)P=SYSCLK2period

(3)FigureshowsonlyPolarity=0,Phase=0asanexample.Tablegivesparametersforallfourmasterclockingmodes.

(4)InthecasewherethemasterSPIisreadywithnewdatabeforeSPIx_ENAdeassertion.

(5)ExceptformodeswhenSPIDAT1.CSHOLDisenabledandthereisadditionaldatatotransmit.Inthiscase,SPIx_SCSwillremain

asserted.

(6)ThisdelaycanbeincreasedundersoftwarecontrolbytheregisterbitfieldSPIDELAY.T2CDELAY[4:0].

(7)IfSPIx_ENAisassertedimmediatelysuchthatthetransmissionisnotdelayedbySPIx_ENA.

(8)InthecasewherethemasterSPIisreadywithnewdatabeforeSPIx_SCSassertion.

(9)ThisdelaycanbeincreasedundersoftwarecontrolbytheregisterbitfieldSPIDELAY.C2TDELAY[4:0].

(10)IfSPIx_ENAwasinitiallydeassertedhighandSPIx_CLKisdelayed.

86PeripheralandElectricalSpecificationsSubmitDocumentationFeedback